### RICE UNIVERSITY

## General-purpose Programming Techniques for Emerging Systems with Non-volatile Byte-addressable Random Access Memory

by

Kumud Bhandari

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree

### **Doctor of Philosophy**

**Approved, Thesis Committee:**

al

Vivek Sarkar, Chair Research Professor in Computer Science

Keith D. Cooper L. John and Ann H. Doerr Professor in Computational Engineering

Peter J. Varman Professor in Electrical and Computer Engineering Professor in Computer Science

Houston, Texas

January, 2018

#### ABSTRACT

General-purpose Programming Techniques for Emerging Systems with Non-volatile Byte-addressable Random Access Memory

by

#### Kumud Bhandari

Emerging byte-addressable non-volatile random access memory (NVRAM) technologies allow persistent data to be accessed and manipulated using CPU load and store instructions. The persistent data in NVRAM can be persisted in the same format as it is manipulated and re-used across execution cycles. In order to achieve this persist-reuse programming idiom, persistent data need to be kept consistent across restarts and tolerated failures, i.e. certain data invariants need to be maintained. As persistent data may be cached in volatile structures such as CPU cache and memory instructions may be reordered, failures or power cycle could violate these invariants and leave persistent data in an inconsistent state. This thesis work explores general-purpose software techniques that minimize the burden on programmers to maintain persistent data consistency under this persist-reuse model. It further focuses on persistent memory management techniques to simplify NVRAM programming. In this aspect, this thesis work identifies and addresses challenges associated with designing a failure-safe and leak-free persistent memory allocator that is also interoperable with various persistent programming libraries. Additionally, it presents software techniques to minimize de-/allocation overhead, avoid persistent leaks, and discusses a memory allocator design approach that enhances the programmability of NVRAM programming libraries. This thesis work shows that these software techniques can

enable the failure-safe use of NVRAM without placing an undue burden on programmers or incurring significant performance overheads.

### Acknowledgments

I thank my Ph.D. thesis advisor Prof. Vivek Sarkar for his invaluable support throughout my Ph.D. studies. I would also like to thank my Ph.D. thesis committee members for their feedback on my thesis to make this thesis better.

I extend my gratitude to the current and past members of the Habanero Extremescale Software team for helping me in numerous ways to conduct my research during my graduate studies. I also thank many student and staff members of the Rice Computer Science Department who have helped and supported me throughout my time at Rice University.

A large portion of this thesis work was carried out at Hewlett-Packard Labs over a number of extended internships during my graduate studies. I would like to thank my mentors at HP Labs Dhruva Chakrabarti, and Hans-J. Boehm for providing me with guidance and support during these internships and beyond. I would also like to thank Haris Volos at HP Labs for helping me evaluate my work against Mnemosyne. I would also like to thank him for sharing his experience and wisdom related to his work on NVRAM. Additionally, I would like to thank Harumi Kuno, Rob Schreiber, Terence Kelly, and Brad Morrey at HP Labs for guidance, support, and fruitful discussions.

This thesis was partially supported by the US Department of Energy under Cooperative Agreement no. DESC0012199 and the Go Fellowship from Oakridge National Lab. I would like to extend my gratitude to Joel Denny, and Jeffrey Vetter for many fruitful meetings and discussions we had related to persistent memory allocation and programming.

# Contents

| Int | roduction                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 | Thesis Scope                                                                                                                                                                                                                                        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.2 | Thesis Statement                                                                                                                                                                                                                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.3 | Contributions                                                                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.4 | Outline                                                                                                                                                                                                                                             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Sur | vey of NVRAM Technologies and Hardware Support                                                                                                                                                                                                      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1 | NVRAM Device Technologies                                                                                                                                                                                                                           | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.2 | Hardware Support                                                                                                                                                                                                                                    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3 | ISA Extensions:                                                                                                                                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.4 | Research Ideas/Prototypes                                                                                                                                                                                                                           | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.5 | Summary                                                                                                                                                                                                                                             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NV  | RAM Persist-Reuse Programming Model                                                                                                                                                                                                                 | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1 | Persistence Designation                                                                                                                                                                                                                             | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.2 | Persistent Data Failure-safe Updates                                                                                                                                                                                                                | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3 | Restart Code                                                                                                                                                                                                                                        | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.4 | Persist-Reuse Model vs. Checkpoint-Restart                                                                                                                                                                                                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.5 | System Assumptions                                                                                                                                                                                                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.6 | Summary                                                                                                                                                                                                                                             | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Co  | mbining Lock-based Approach with Copy-on-Write for                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NV  | RAM Persistency                                                                                                                                                                                                                                     | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | <ol> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>1.4</li> <li>Sur</li> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>NV</li> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>Col</li> </ol> | 1.2       Thesis Statement.          1.3       Contributions          1.4       Outline          Survey of NVRAM Technologies and Hardware Support         2.1         NVRAM Device Technologies          2.2       Hardware Support          2.3       ISA Extensions:          2.4       Research Ideas/Prototypes          2.5       Summary          Summary         2.5         NVRAM Persist-Reuse Programming Model         3.1       Persistence Designation          3.2       Persistent Data Failure-safe Updates          3.3       Restart Code          3.4       Persist-Reuse Model vs. Checkpoint-Restart          3.5       System Assumptions |

|   | 4.1  | Log-ba  | sed Transactional Approach vs. Copy-on-Write      | 19 |

|---|------|---------|---------------------------------------------------|----|

|   | 4.2  | Lack o  | f NVRAM Applications                              | 19 |

|   | 4.3  | Contri  | butions                                           | 20 |

|   | 4.4  | Atlas F | Programming Library                               | 20 |

|   |      | 4.4.1   | Failure Atomic Section and Consistency Guarantees | 20 |

|   |      | 4.4.2   | Compiler Instrumentation and Runtime              | 21 |

|   |      | 4.4.3   | Failure, Restart, and Recovery                    | 22 |

|   | 4.5  | MDB-N   | NVM: NVRAM Key-value Store                        | 23 |

|   |      | 4.5.1   | Programming Interface                             |    |

|   |      | 4.5.2   | Internal Structure                                | 26 |

|   |      | 4.5.3   | Persistent Memory Management                      | 29 |

|   |      | 4.5.4   | Read-Only Transactions                            | 30 |

|   |      | 4.5.5   | Read-Write Transactions                           | 31 |

|   | 4.6  | MDB v   | vs. MDB-NVM                                       | 33 |

|   | 4.7  | Metho   | dology                                            | 33 |

|   | 4.8  | Benchi  | marks                                             | 34 |

|   | 4.9  | Results | 5                                                 | 35 |

|   | 4.10 |         | d Work                                            | 36 |

|   | 4.11 | Summa   | ary                                               | 37 |

|   |      |         |                                                   |    |

| 5 | Rec  | overa   | ble Allocation of Non-volatile Memory             | 39 |

|   | 5.1  | Contri  | butions                                           | 40 |

|   | 5.2  | Backgr  | ound                                              | 41 |

|   |      | 5.2.1   | Architectural Assumptions                         | 41 |

|   |      | 5.2.2   | Programming Assumptions                           | 42 |

|   |      | 5.2.3   | Terminology                                       | 43 |

|   | 5.3  | NVRA    | M Allocator Challenges                            | 43 |

|   |      | 5.3.1   | Failure-Induced Inconsistencies                   | 44 |

|     | 5.3.2  | Transient vs. Persistent Metadata                | 44 |

|-----|--------|--------------------------------------------------|----|

|     | 5.3.3  | Online Failure Consistency Overhead vs. Recovery | 45 |

|     | 5.3.4  | Safe Deallocation                                | 45 |

| 5.4 | Overv  | iew of the Approach                              | 46 |

|     | 5.4.1  | Integrated De-/allocation and Garbage Collection | 46 |

|     | 5.4.2  | Choosing Persistent Metadata                     | 47 |

|     | 5.4.3  | APIs Provided by Makalu                          | 48 |

|     | 5.4.4  | Comparison with Existing NVRAM Allocators        | 48 |

| 5.5 | Intern | al Structures and Layouts                        | 51 |

|     | 5.5.1  | Persistent Block Header                          | 52 |

|     | 5.5.2  | Persistent Header Map                            | 53 |

|     | 5.5.3  | Persistent Log Space                             | 54 |

|     | 5.5.4  | Persistent Roots                                 | 54 |

|     | 5.5.5  | Persistent Base Metadata                         | 54 |

|     | 5.5.6  | Transient Chunk Freelists                        | 55 |

|     | 5.5.7  | Transient Object Freelists                       | 55 |

|     | 5.5.8  | Transient Reclaim Lists                          | 55 |

| 5.6 | Alloca | tion                                             | 56 |

|     | 5.6.1  | Refilling an Empty Freelist                      | 56 |

|     | 5.6.2  | New Block Allocation                             | 57 |

|     | 5.6.3  | Large Object Allocation                          | 58 |

|     | 5.6.4  | Expansion of Heap Space                          | 58 |

| 5.7 | Deallo | ocation                                          | 58 |

|     | 5.7.1  | Object Freelists Truncation                      | 59 |

|     | 5.7.2  | Empty Block Deallocation                         | 60 |

|     | 5.7.3  | Large Object Deallocation                        | 60 |

| 5.8 | ACID   | Guarantees for Metadata                          | 60 |

|     | 5.8.1  | Eventual Visibility for Metadata                 | 64 |

|   | 5.9  | Offline        | Recovery and GC                                     | 64 |

|---|------|----------------|-----------------------------------------------------|----|

|   |      | 5.9.1          | Recovery                                            | 64 |

|   |      | 5.9.2          | Garbage Collection                                  | 65 |

|   | 5.10 | Execut         | tion Stages and Failure Mitigation                  | 66 |

|   |      | 5.10.1         | One-Time Online Initialization                      | 66 |

|   |      | 5.10.2         | Online Re-initialization                            | 66 |

|   |      | 5.10.3         | Online Execution                                    | 67 |

|   |      | 5.10.4         | Offline Recovery                                    | 67 |

|   | 5.11 | Integra        | ation with NVMPL                                    | 68 |

|   |      | 5.11.1         | NVMPL Facing Interfaces                             | 68 |

|   |      | 5.11.2         | Integration with Atlas and Mnemosyne                | 68 |

|   | 5.12 | Related        | d Work                                              | 69 |

|   | 5.13 | Evalua         | tion                                                | 70 |

|   |      | 5.13.1         | Comparison with Existing Allocators                 | 71 |

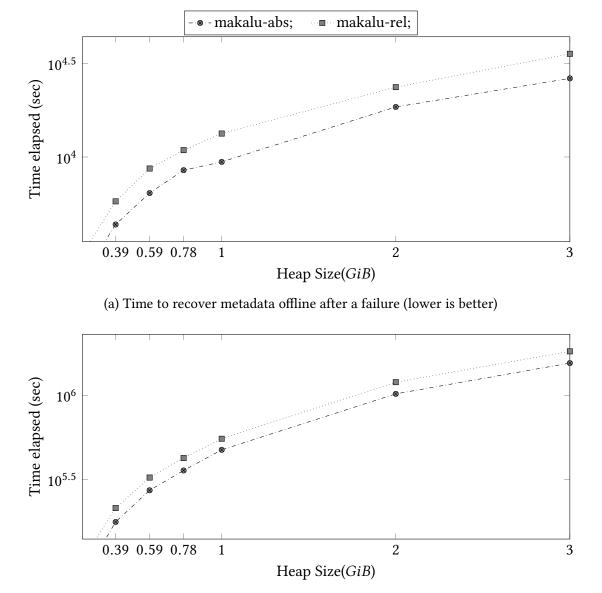

|   |      | 5.13.2         | Recovery and Garbage Collection                     | 73 |

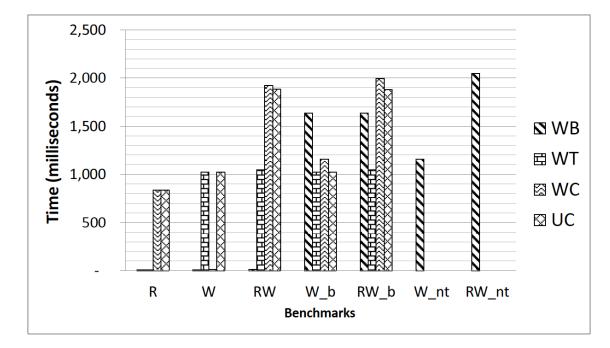

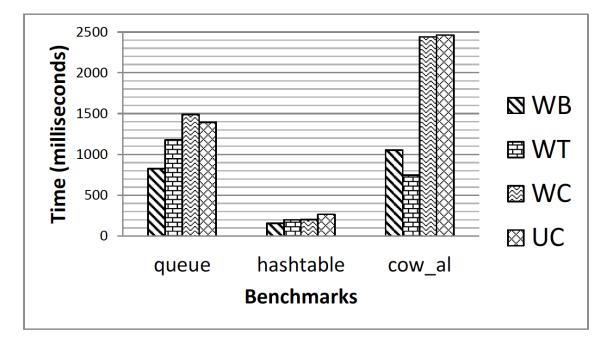

|   |      | 5.13.3         | Comparison with NVMPL Default Allocators            | 77 |

| 6 | Rel  | ative <b>A</b> | Addressing and Precise Garbage Collection of Persis | -  |

|   | ten  | t Heap         | os Using Persistent Types                           | 84 |

|   | 6.1  | Contri         | butions                                             | 86 |

|   | 6.2  | Backgr         | round                                               | 86 |

|   |      | 6.2.1          | Architectural Assumptions                           | 86 |

|   |      | 6.2.2          | Programming Assumptions                             | 86 |

|   |      | 6.2.3          | Terminology                                         | 87 |

|   | 6.3  | Challe         | nges                                                | 87 |

|   | 6.4  | Overvi         | iew of Our Approach                                 | 88 |

|   |      | 6.4.1          | Makalu-rel APIs                                     | 88 |

|   | 6.5  | Interna        | al Structures and Layouts                           | 89 |

|   |      | 6.5.1   | Persistent Block Header                                   | 89 |

|---|------|---------|-----------------------------------------------------------|----|

|   |      | 6.5.2   | Persistent Header Map                                     | 89 |

|   |      | 6.5.3   | Persistent Base Metadata                                  | 90 |

|   | 6.6  | Reduci  | ng Address Translation Overhead                           | 90 |

|   | 6.7  | Allocat | tion                                                      | 92 |

|   | 6.8  | Deallo  | cation                                                    | 92 |

|   | 6.9  | Failure | Consistency Guarantees                                    | 92 |

|   | 6.10 | Offline | Recovery and Garbage Collection                           | 94 |

|   |      | 6.10.1  | Precise Parallel Mark Algorithm                           | 94 |

|   | 6.11 | Interac | tion with NVRAM programming libraries                     | 96 |

|   |      | 6.11.1  | Online Start                                              | 96 |

|   |      | 6.11.2  | Offline Restart and Recovery                              | 96 |

|   |      | 6.11.3  | Online restart                                            | 97 |

|   | 6.12 | Evalua  | tion                                                      | 97 |

|   |      | 6.12.1  | Allocation Performance Comparisons                        | 98 |

|   |      | 6.12.2  | Comparison Using Scientific Applications                  | 99 |

|   |      | 6.12.3  | Comparison: Conservative vs. Precise Garbage Collection 1 | 02 |

|   | 6.13 | Related | l Work                                                    | 03 |

|   | 6.14 | Summa   | ary                                                       | 03 |

| 7 | Fut  | ure W   | ork and Conclusion 10                                     | )7 |

|   | 7.1  | Future  | Work                                                      | 07 |

|   | 7.2  | Conclu  | usions                                                    | 08 |

| A | ppen | dices   | 11                                                        | 1  |

A CPU Caching Policy Implications in Pre-NVRAM Architecture 112

| A.1 | Caching Policy Choices: Write Back vs. Write-Through |

|-----|------------------------------------------------------|

| A.2 | Contributions                                        |

| A.3 | Description of Our Approach                          |

| A.4 | Methodology                                          |

|     | A.4.1 Linux Kernel Modification                      |

| A.5 | Benchmarks                                           |

| A.6 | Results                                              |

| A.7 | Related Work                                         |

| A.8 | Summary                                              |

# References

124

# List of Figures

| 3.1  | A Simplified Architectural Model                     | 11 |

|------|------------------------------------------------------|----|

| 3.2  | Persist-Reuse Example                                | 17 |

|      |                                                      |    |

| 4.1  | MDB-NVM API                                          | 24 |

| 4.2  | MDB-NVM Example                                      | 27 |

| 4.3  | MDB-NVM Initialization                               | 28 |

| 4.4  | MDB-NVM Transaction Commit                           | 32 |

| 4.5  | MDB-NVM: Comparision with Disk-based performance     | 38 |

| 4.6  | MDB-NVM: Cost of Persistence                         | 38 |

|      |                                                      |    |

| 5.1  | Persistent Heap Snapshot                             | 42 |

| 5.2  | Allocation with NVMPL's default allocator            | 49 |

| 5.3  | Allocation with nvm_malloc                           | 50 |

| 5.4  | Allocation with Makalu                               | 50 |

| 5.5  | Structure of the block header                        | 52 |

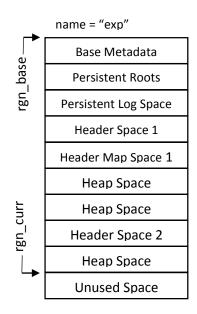

| 5.6  | Layout of Makalu in an NVRAM region                  | 53 |

| 5.7  | Pseudocode for empty block deallocation              | 61 |

| 5.8  | Internal facility for failure-atomic updates         | 63 |

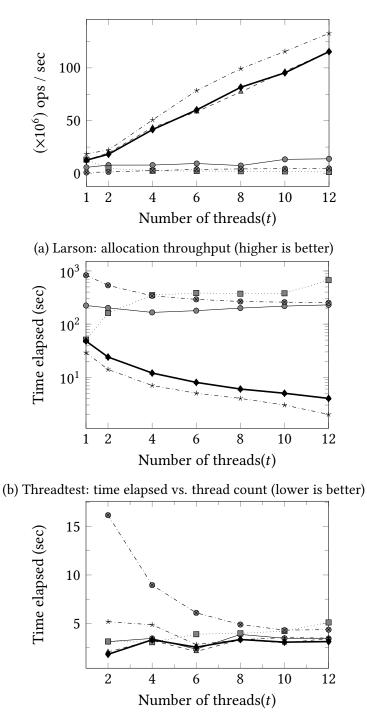

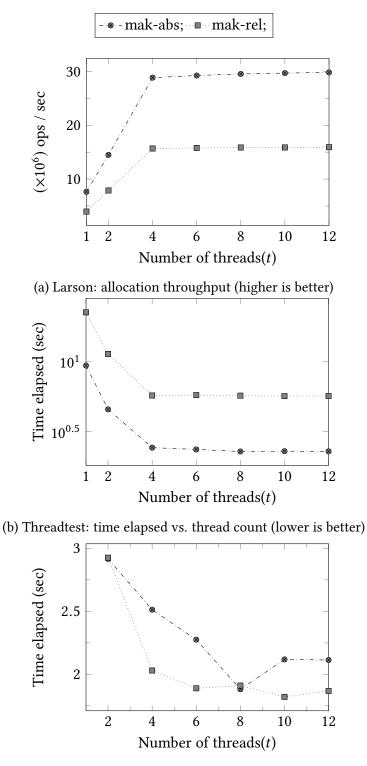

| 5.9  | Allocation benchmarks Performance                    | 74 |

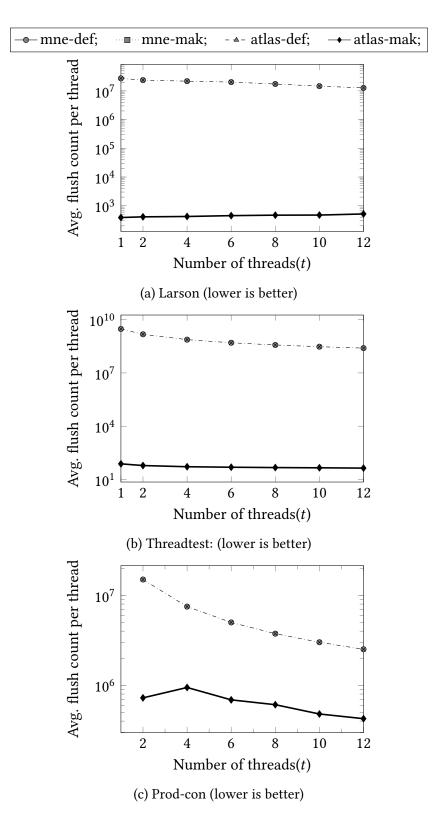

| 5.10 | Allocation Benchmarks Flushes                        | 75 |

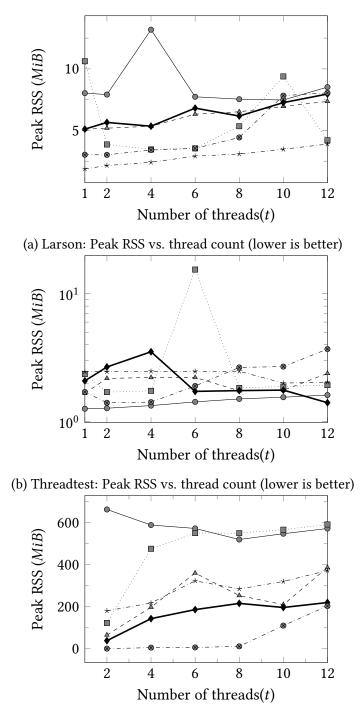

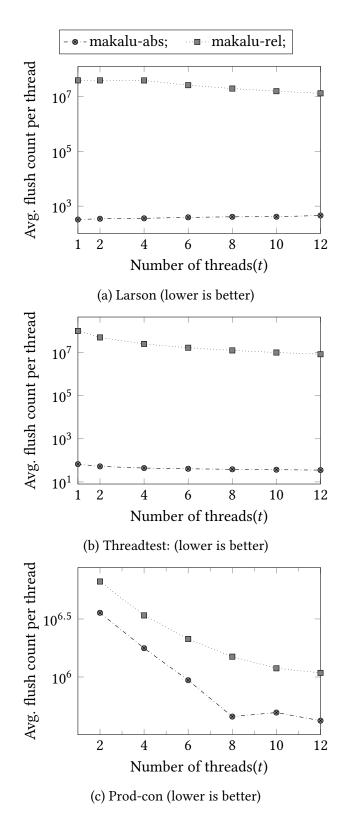

| 5.11 | Allocation Benchmarks Memory Consumption             | 81 |

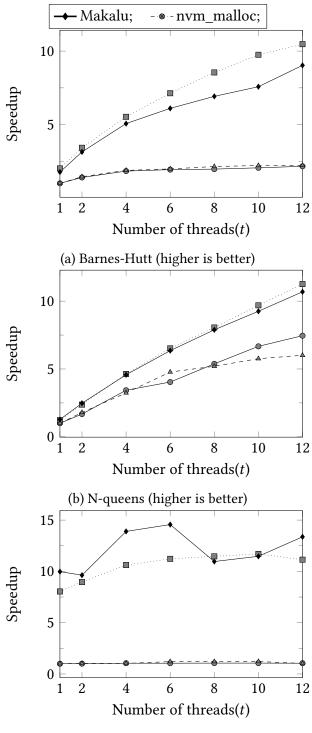

| 5.12 | Performance: Makalu as Programming Library Allocator | 82 |

| 5.13 Performance: Makalu as Programming Library Allocator (full consistency) 83 | 5.13 | Performance: | Makalu as | Programming | Library | Allocator | (full consistency) | 83 |

|---------------------------------------------------------------------------------|------|--------------|-----------|-------------|---------|-----------|--------------------|----|

|---------------------------------------------------------------------------------|------|--------------|-----------|-------------|---------|-----------|--------------------|----|

| 6.1  | Installing a new block header in Makalu-rel | 89  |

|------|---------------------------------------------|-----|

| 6.2  | Looking up a header from header cache       | 91  |

| 6.3  | Creating undo log using relative address    | 93  |

| 6.4  | Replay of Undo logs with relative addresses | 93  |

| 6.5  | Mark Stack Entry for Offline GC             | 94  |

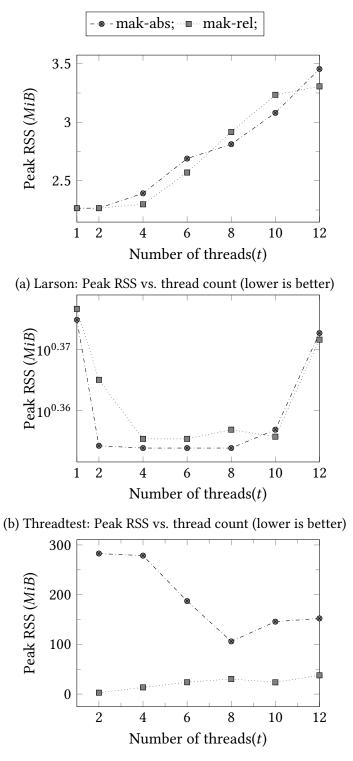

| 6.6  | Allocation benchmarks Performance           | 100 |

| 6.7  | Allocation Benchmarks Flushes               | 101 |

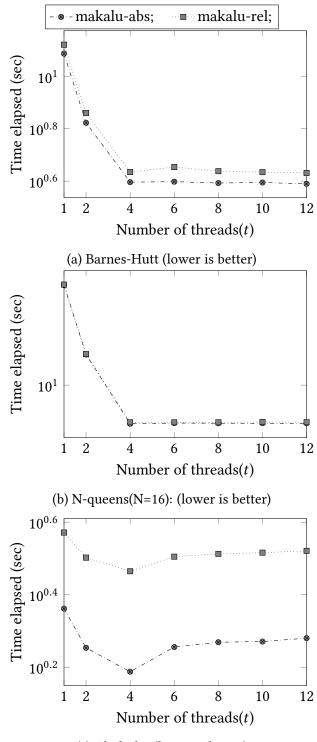

| 6.8  | Allocation Benchmarks Memory Consumption    | 104 |

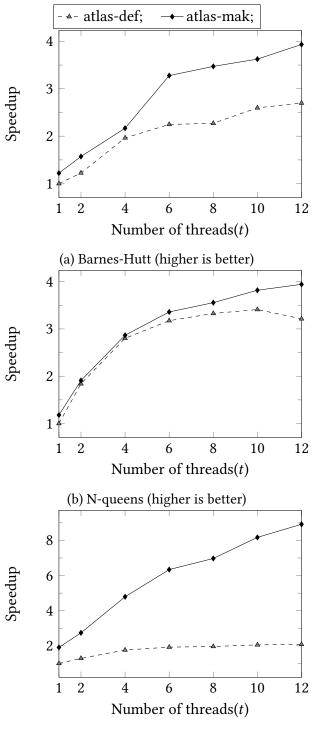

| 6.9  | Comparion using scentific applications      | 105 |

| 6.10 | Comparion of Recovery and GC time           | 106 |

|      |                                             |     |

| A.1  | A Simple Program Sequence                   | 119 |

| A 0 | Caching policy synthetic benchmarks      | 110 |

|-----|------------------------------------------|-----|

| A.2 |                                          | 119 |

| A.3 | Caching policy data structure benchmarks | 121 |

### Chapter 1

### Introduction

Limitations in current DRAM technology scaling [1–3] have prompted research in alternate memory technologies. Almost all alternatives being explored such as Memristor [4], Phase Change Memory (PCM) [5,6], and 3D XPoint [7] are non-volatile in nature. Such nonvolatile memory (NVRAM) combines the byte-addressability of DRAM with the persistence of hard disks. In the near future, NVRAM may at least partially replace DRAM, making persistent data accessible through CPU load and store instructions. With NVRAM, persistent data can be manipulated in the same format as stored, thus requiring no expensive and cumbersome conversion. Consider an example where a linked list has to be saved in a traditional filesystem in the absence of NVRAM. Such a linked-list has to be serialized into a stream of bytes representing its state to save to a file and deserialized later on before the CPU can again access the data in some later time, possibly after a system restart. With NVRAM, a programmer can write code that can directly allocate persistent linked-list nodes, and manipulate this single copy of the linked-list. Thus, NVRAM opens up an opportunity to have in-memory object persistence so that program states that outlive the creating process can be preserved, shared, and reused. Using this persist-and-reuse model, a quick restart of an application from an intermediate state appears a reality. While starting, an application looks for existing data that it can reuse. If present, the application adjusts its context and instead of computing from scratch, merely reuses the existing data for the rest of its computation.

Although using NVRAM as traditional volatile memory is trivial, taking advantage of inmemory durability is challenging in the presence of system failures. Updates to persistent data may not become visible to NVRAM in the order intended due to volatile CPU caches or store re-ordering allowed by the memory model. As a result, an interruption such as a power failure may introduce inconsistencies (e.g. dangling pointer) to persistent data in NVRAM. This thesis work addresses several aspects of NVRAM programming such as failure resilient storage of user data in NVRAM, and persistent memory management with the central goal of enabling programmers to take advantage of persistence provided by NVRAM while minimizing the direct programming burden on them.

### 1.1 Thesis Scope

System experts may choose to exploit persistence provided by NVRAM in a highly specialized setting such as to improve database performance [8] or to design in-memory filesystems [9]. In contrast to such specific use cases of NVRAM, this thesis discusses techniques to make persistence provided by NVRAM accessible to programmers for general purpose programming. Using software techniques described in this thesis work, programmers can allocate and store everyday data structures such as a linked-list or a queue in NVRAM, and reuse them across system restarts by adjusting the programming context based on the state of the persistent data. In this direction, this thesis work discusses low-overhead techniques for developing applications to take advantage of NVRAM persistence, addresses challenges in managing persistent memory and identifies the interplay that exists between persistent memory approach and NVRAM programmability.

### 1.2 Thesis Statement

Advances in programming models and system software for NVRAM can enable fault-tolerant use of NVRAM without placing an undue burden on programmers or incurring significant performance overheads.

### **1.3 Contributions**

This dissertation makes the following contributions:

- A novel approach for failure consistency that combines lock-based transactional semantics with copy-on-write. We show that copy-on-write mechanism can be combined with lock-based transactional semantics to reduce performance overhead while maintaining programmability

- A design and implementation of a real-world NVRAM application. We designed and implemented an NVRAM version of the commercially used MDB key-value store and characterized its performance overheads

- The first published detailed assessment of the challenges involved in designing an interoperable, leak-free persistent memory allocator.

- The first published leak-free persistent memory allocator that is interoperable with numerous NVRAM programming library. To the best of our knowledge, we present the design and the implementation of the first NVRAM memory allocator that is drop-in replaceable with C/C++ standard malloc/free, that is leak-free and can be used with various existing NVRAM libraries.

- A novel offline recovery and conservative garbage collection approach to prevent failure-induced leaks, and reduce the online cost of de-/allocation.

- A novel approach for precise offline garbage collection over relative heap addresses using persistent type information.

### 1.4 Outline

The rest of this dissertation is organized as follows:

- Chapter 2 presents a survey of emerging NVRAM technologies, their performance characteristics and extensions in Instruction Set Architecture (ISA) to facilitate NVRAM programming

- Chapter 3 introduces persist-reuse model for NVRAM programming and compares it with other traditional approaches to persistence such as checkpoint-restart and orthogonal persistence

- Chapter 4 presents a novel approach to failure consistency that combines a lockbased transactional approach with a copy-on-write mechanism to reduce persistence overhead. It also presents the design and implementation of an NVRAM version of the MDB key-value store, a commercially used backend for OpenLDAP.

- Chapter 5 presents an assessment of challenges associated with designing a leak-free interoperable persistent memory allocator and the design of such a memory allocator for NVRAM

- Chapter 6 presents the design and the implementation of memory allocator that supports relative addressing and precise garbage collection based on persistent types

- Finally, chapter 7 presents future work and conclusion

### **Chapter 2**

### Survey of NVRAM Technologies and Hardware Support

### 2.1 NVRAM Device Technologies

Several different device technologies are being explored by hardware manufacturers to make NVRAM available in future systems. Some of these technologies which have been productized are described below [10]:

- *Ferroelectric RAM (FRAM):* uses ferroelectric capacitor formed from a common ferroelectric material to store bits represented by two reversible polarization states.

- *Magnetic RAM (MRAM):* uses a two-layer magneto-resistive structure for data storage and measures the resultant difference in resistance between the layers to readout information.

- *Spin Transfer Torque RAM (STTRAM):* uses a spin-polarized current to modify the orientation of a magnetic layer in a magnetic tunnel junction (two ferromagnetic layers separated by a thin insulator) to store bits.

- *Phase Change Memory (PCRAM):* uses two reversible phases amorphous and the crystalline states of chalcogenide glass.

Given the differences in underlying technologies, future NVRAM devices may vary in their access times. Table 2.1 lists access times – both write (W) and read (R) – for various

| Device Types      | FRAM    | MRAM    | STTRAM  | PCRAM    |

|-------------------|---------|---------|---------|----------|

| Access Time (W/R) | 50/75ns | 12/12ns | 10/10ns | 100/20ns |

Table 2.1: Access times for various NVRAM device technologies [10]

| Device Types      | NAND Fash | HDD       | DRAM    |

|-------------------|-----------|-----------|---------|

| Access Time (W/R) | 200/25 us | 9.5/8.5ms | 10/10ns |

Table 2.2: Access times for various traditional device technologies [10]

NVRAM device technologies. Table 2.2 lists access times for DRAM, magnetic hard disk drive (HDD) and NAND Flash block devices for comparison. As seen from these tables, many technologies such as STTRAM and MRAM have access latencies comparable to the current DRAM technology. Others such as PCRAM have higher write latency but are still orders of magnitude better than NAND Flash or HDD. The endurance of these devices also vary. PCRAM, for instance, have endurance similar to NAND Flash (10<sup>5</sup> cycles) whereas FRAM, MRAM, and STRAM have endurance similar to DRAM (10<sup>16</sup> cycles) [10]. Unlike DRAM which has retention of 64ms (without refresh), NVRAM devices listed in table 2.1 have retention same as NAND Flash devices ( 10 years). Addressing device endurance and wearability is beyond the scope of this thesis.

### 2.2 Hardware Support

Traditionally, CPU cache, in general, is functionally invisible to a program that manipulates data in DRAM. The stores from a CPU can become visible in DRAM out of program order as long as memory consistency model along with cache coherence protocol ensures that it becomes visible to other CPUs in a correct order. This may not be true for data stored in NVRAM. In future systems, data stored in NVRAM is expected to be accessible using CPU load and store instructions. Consider an example below where some data is being written before the valid bit is being set.

- 1: store data "moon"

- 2: store valid "1"

If store 2 becomes visible in persistent domain (e.g. NVRAM) and power recycle occurs while store 1 is only present in a transient domain, e.g. CPU cache, the persistent data invariant is violated as a valid bit is set when the data field in NVRAM contains garbage. Therefore, being able to order stores visibility to NVRAM is crucial to maintaining persistent data consistency. Given volatile write-back CPU caches may continue to exist in future systems with NVRAM and may cache persistent data updates, a persistent memory application needs to be able to make these cache lines visible in NVRAM in a correct order.

#### 2.3 ISA Extensions:

Intel x86-64 ISA traditionally provides CLFLUSH instruction to invalidate a cache line by its virtual address such that it gets eventually written back to the memory system. This instruction is supported by most Intel x86-64 bit CPUs. This instruction has several drawbacks. First, it stalls the CPU pipeline and thus serializes the execution. Second, it invalidates the cache line, thus next read/write to the cache line is a miss. Lastly, it only evicts data to the memory subsystem and does not guarantee that the data has reached the persistent domain.

In anticipation of NVRAM, Intel announced an extension to its x86-64 bit ISA [11], which includes CLFLUSHOPT, an optimized version of CLFLUSH. Unlike CLFLUSH, it does not stall CPU (unordered) and thus the execution of one or more CLFLUSHOPT may overlap. A CLFLUSH operation is only ordered by a full memory fence (e.g. MFENCE), whereas CLFLUSHOPT is ordered by store fence (e.g SFENCE). Intel also introduced another instruction, namely CLWB, which is ordered by SFENCE and writes back a cache line without invalidating it.

All the instructions mentioned above ensures that a cache line reaches a write pending queue (WPQ) in the memory controller. In Intel systems with NVRAM, WPQ is expected to be in the persistent domain. In this light, Intel deprecated the instruction PCOMMIT which was introduced briefly as a means to flush WPQ in systems where WPQ in a memory controller was not incorporated into the persistent domain. Combination of CLWB and SFENCE is enough to order the visibility of persistent stores in Intel architecture where WPQ is in the persistent domain [12]. This is expected to be the case for all future systems with NVRAM.

Likewise, ARM has introduced an instruction DC CVAP to clean virtual address to the point of persistency in Armv8.2 [13].

### 2.4 Research Ideas/Prototypes

Several ideas have been proposed to make persistent stores visible in NVRAM while exposing persistent stores concurrency as much as possible at the hardware level. We discuss some of them below.

**Epoch Barrier:** Condit et al. proposed a hardware modification in CPU cache to separate persistent writes into epochs [14]. A set of writes are separated into epoch by epoch barrier. Each cache line is tagged with epoch id. Whenever a cache line belonging to a specific epoch is evicted, it triggers cascading writes of all cache lines belonging to earlier epochs. This approach requires tagging cache line with epoch id and tracking oldest in-flight epoch per CPU.

**Strand Persistency:** Pelley et. al. suggest a mechanism where a set of stores from the same CPU are divided into strands by a strand barrier [15]. Stores from different strands are made visible concurrently. Within a strand, persist barrier can be used to order store visibility. This approach requires store dependence tracking at the hardware level for ordering requirements.

### 2.5 Summary

The access latency for most future NVRAM devices seems to be similar to DRAM. Furthermore, with the extension of persistence domain to the memory controller and write pending queue within it (as seems to be the case for Intel architecture), write latency of actual NVRAM devices may not be of a large concern to persistent memory programmers.

ISA architecture is continuously evolving to enable programmers to use NVRAM as a byteaddressable persistent medium without incurring a large performance penalty for keeping persistent data consistent across power recycles and failures. Systems with extended architecture and NVRAM are still not widely available to programmers and researchers, and the ISA itself appears to be continually evolving. Several other approaches requiring hardware modifications have been proposed but are limited to research ideas or prototypes. A large body of work on programming models and programming libraries predates these ISA extensions. Simulation-based studies are equally likely to be inaccurate in the face of evolving device technology and system architecture. Hence, in the absence of extended ISA and/or due to lack of wide availability of new hardware support, programming library and runtime developers/researchers have largely relied on existing instructions such as CLFLUSH and MOVNTQ (move with non-temporal hint) to design programming libraries for NVRAM and to roughly estimate their performance [16–19]. This may change in the future with better access to new hardware.

### Chapter 3

### **NVRAM Persist-Reuse Programming Model**

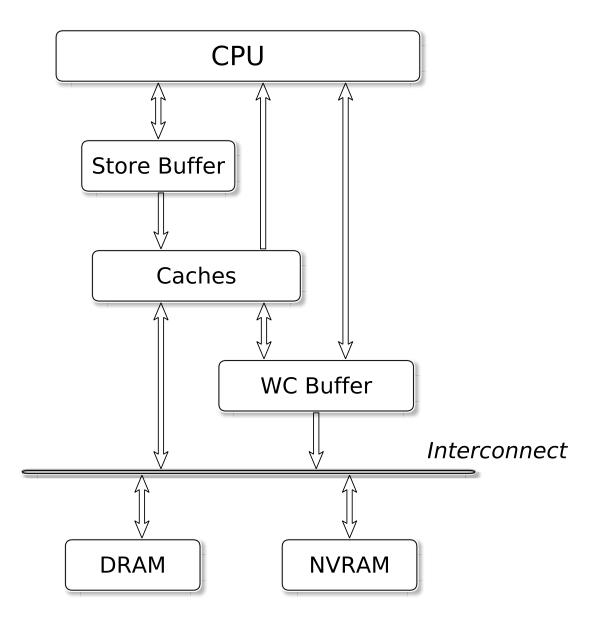

Persistent data stored in NVRAM are useful only if they are consistent; in particular, their invariants must be preserved. Even in the presence of NVRAM, there will be volatile buffers and caches in the memory hierarchy, simply because of the performance advantages they provide. This implies that during program execution, some of the states may reside in volatile structures and the rest in NVRAM. Figure 3.1 shows a simplified version of the architectural model that we assume; it is in part based on the Intel x86-64 architecture [20]. The CPU core may temporarily keep each store to memory in a store buffer. The store buffer improves performance by hiding the latency of cache and memory accesses. Certain instructions such as memory fences result in draining the store buffer. As shown in figure 3.1, we assume that DRAM and NVRAM may co-exist in the same memory system.

As figure 3.1 shows, even in the presence of NVRAM, volatility remains an important part of the memory hierarchy. If the program crashes because of a hardware or power failure, only the state present in NVRAM at the time of the crash will survive a restart. Any state that was present in volatile structures at the time of the crash is lost. Hence, the challenge is to ensure that at any point of program execution, there is enough information on NVRAM to reconstruct a consistent state of the program data structures.

Using low-level hardware primitives described in chapter 2 to maintain the consistency of persistent data stored in NVRAM diminishes programmability. Several NVRAM programming libraries have been developed which enable programmers to maintain persistent data in NVRAM and manipulate them in a fail-safe manner [16, 17, 21]. These independently developed libraries support the common persist-reuse model described below. Figure 3.2 shows pseudocode written using this persist-reuse model.

Figure 3.1: A Simplified Architectural Model

### 3.1 Persistence Designation

An NVRAM application may persist one or more data structures such as a queue, an array or other program variables in NVRAM. Such a data structure is designated as persistent by explicitly allocating it in NVRAM.

This approach is in contrast with earlier pre-NVRAM persistence programming models such as orthogonal persistence [22]. In orthogonal persistence, all objects were allocated the same way, and hence all allocated objects are potentially persistent. The persistence is based on the liveness of the variable and/or its reachability from other persistent objects. This required pointer reachability analysis at different program points incurring performance penalties. Furthermore, transient objects such as network sockets, and user passwords may undesirably become persistent under such a scheme. Such undesirable persistence of data also unnecessarily increases the size of persistent data. Under the persist-reuse model described here, only the user-desired data becomes persistent. However, this puts a burden on a programmer to correctly identify such persistent objects. In the example in figure 3.2, line 1 shows a node of a persistent queue being explicitly allocated.

### 3.2 Persistent Data Failure-safe Updates

Persistent data in NVRAM is stored in the same format as it is manipulated. This single format makes it possible to manipulate often times a single copy of persistent data in NVRAM directly using CPU load/store instructions. Such modifications need to take place in a failure-safe manner. In an example in figure 3.2, the node allocated in line 1 is being initialized in 2, and finally being attached to persistent queue in NVRAM in lines 4–7. In this example, stores associated with lines 1, 2 and 3 need to be visible in NVRAM before stores in lines 4–7. Additionally, stores from 4–7 need to be visible in NVRAM on-all-or-nothing basis w.r.t failures and power recycle.

A programming library implementing this programming model may provide tools to the programmer to identify a section of code that requires failure safety guarantees. The library may then enforce proper ordering and atomicity of stores based on programmer directives. Mnemosyne, one such NVRAM programming library that implements this programming model, for instance, offers software transactional memory to programmers as a means to enforce failure atomicity. As the readers will observe in the following chapters, the failure atomicity and store ordering can also be largely inferred automatically for certain class of legacy code.

This approach is also different than the approach taken traditional orthogonal persistence. To uphold the design principle of "persistence independence", orthogonal persistence allows a programmer to write code independent of persistence or potential persistence of the data that the code manipulates [22].

### 3.3 Restart Code

The central goal of failure safe updates mentioned in the previous section to transition persistent data stored in NVRAM from one consistent state to another. The programmer is responsible for writing restart code that adjusts the programming context after failure or power recycle based on the consistent persistent data in NVRAM. A restart code is never expected to see an inconsistent version of the persistent data. Depending on the implementation strategy, the library implementation of the programming model may use some post-failure recovery logic (e.g persistent logs replay) to restore the state of the persistent data in NVRAM to a consistent state before user-written restart code accesses such data. In the example in figure 3.2, restart code in lines 8–9 re-initializes the head and tail pointers of a queue with values from NVRAM.

### 3.4 Persist-Reuse Model vs. Checkpoint-Restart

Persist-Reuse Model is much different that system level checkpoint- restart (SLC) and closer to application-level checkpoint-restart (ALC). In SLC, a programmer may be able to define the frequency of checkpoint, but since the checkpointing happens usually at the OS level, the whole state of execution is usually saved as a snapshot [23]. Such a snapshot may contain register states, call stack, program variables and so on. The persist-reuse model is

much more focused on the state of the certain application data rather than the state of the whole execution.

Some similarities exist between ALC [24] and persist-reuse model in the sense that programmer much more control over what program variables and data are important to be saved for later use. However, the emphasis of ALC to recreate the state of computation to last check-pointed state on restart. As a result, ALC may still need to save more information about transient program states, which is not typically done under the persist-reuse model. Persist-reuse model is much data-centric (as opposed to execution-centric) in the sense that persist-reuse model only concerns with advancing the state of persistent data in NVRAM. For example, 10 threads may be adding nodes to a persistent queue under persist-reuse model before a failure occurs. When the application restarts, it initializes from the last consistent state of the queue (i.e. queue with a certain number of nodes added to it) before the failure occurred and may resume with a single thread or 20 threads. Alternatively, unlike the ALC, persist-reuse model does not necessarily attempt to recreate the exact execution scenario before failure. Furthermore, the persist-reuse model allows a single copy of user data to be continually updated and the same copy becoming the basis of restart later. This is also not the case with checkpoint-restart where a snapshot is stored separately in a possibly different format and never manipulated directly.

### 3.5 System Assumptions

In the face of evolving hardware architecture, much of the contemporary work on the persist-reuse programming model for NVRAM (e.g. Mnemosyne, NV-Heaps, Atlas, Pmem.io) make following general assumptions about the underlying hardware. It is assumed that the access latency of durable data stored in NVRAM is comparable to transient data stored in DRAM. At the lowest level, initial NVRAM devices may make trade-offs resulting in write latencies appreciably longer than DRAMas discussed in chapter 2. But this increased latency may not be user visible. It appears likely that memory controllers will have enough capacitive power backup such that write requests, once accepted by the memory controller, can be

viewed as persistent. A recent decision by Intel to ensure that persistence domain extends to write pending queue in memory controller seems to confirm this case for the future (see chapter 2) [12]. Even if the power and the CPU die, the controller will ensure that accepted requests are written. Hence, the actual write latency to the NVRAM device may not matter for our purposes. Hence, unless otherwise noted, NVRAM is simulated by DRAM using Linux RAM disk [25] throughout this thesis work.

This thesis work, similar to other related work on persist-reuse programming model, also assumes that persistent data stored in DRAM and transient data stored in NVRAM are addressed using the same virtual address space.

A fail-stop model is assumed throughout this thesis and does not address partial failure scenarios. If a component of a system fails, the whole system is expected to fail. Process crash, power outage are all assumed as tolerated failures and once such failure happens, the system halts until it is restarted.

The work in this thesis, along with much of the related work, uses CLFLUSH and MFENCE instructions when estimating persistence programming performance overhead instead of new cache management instructions described in section 2.3. This approach is taken for the following two reasons. First, actual hardware with extended ISA is not widely available. Second, almost all of the related work (e.g. Mnemosyne, Atlas, nvm\_malloc) against which we can compare our work use CLFLUSH instructions instead of the new instructions and thus doing so makes it a fair comparison. These performance estimates using CLFLUSH are rather pessimistic, and throughout this thesis, we describe why we expect the overhead estimate to decrease (not increase) and the performance to improve with new and better ISA.

### 3.6 Summary

The anticipation of NVRAM being widely available has inspired a persist-reuse programming model that is quite different than the traditional approaches to persistence such as orthogonal persistence and checkpoint-restart. Persist-reuse enables single-copy update and checkpointing as opposed to snapshot based checkpointing. It also streamlines the persistent data needed to restart a program after a failure or power cycle. Unlike in the implementation of orthogonal persistence, it does not require expensive reachability-based analysis to determine what variables and states need to be persisted at various program points.

```

/* allocate */

1: Node* t_tmp = nvm_alloc(sizeof(Node));

/* initialize */

2: t_tmp->val = 10;

3: t_tmp->next = NULL;

/* publish */

4: BEGIN FAILURE ATOMIC SECTION

5: p_queue->tail->next = t_tmp;

6: p_queue->tail = t_tmp;

7: END FAILURE ATOMIC SECTION

/* user written restart code */

8: p_queue->head = NVM_root(0);

9: p_queue->tail = NVM_root(1);

```

Figure 3.2: A sample pseudocode showing persist-reuse model.

### Chapter 4

# Combining Lock-based Approach with Copy-on-Write for NVRAM Persistency

Persistent data stored in emerging NVRAM, can be accessed directly through CPU load and store instructions. This means that the persistent data is being stored in the same format as it is being manipulated, thus requiring only a single copy of data to be maintained, and avoiding expensive and cumbersome conversion.

NVRAM opens up an opportunity to have in-memory object persistence so that program states that outlive the creating process can be preserved, shared, and reused [16, 17, 19]. Using this persist-and-reuse model, a quick restart of an application from an intermediate state appears a reality. While starting, an application looks for existing data that it can reuse. If present, the application adjusts its context and instead of computing from scratch, merely reuses the existing data for the rest of its computation.

Persistent data must be updated with great care so as to be reusable. Otherwise, updates may become visible to NVRAM only partially, or not in the intended order. This may happen as a result of failures in the middle of critical sections, volatile CPU caches, or out-oforder cache evictions. As a result, an interruption such as a power failure may introduce inconsistencies (e.g. dangling pointers) to persistent data in NVRAM. Hence, some set of critical updates to persistent data must be applied on an all-or-nothing basis, and in the correct order with respect to other updates, to guarantee the consistency of in-memory persistent data.

### 4.1 Log-based Transactional Approach vs. Copy-on-Write

Prior work [16, 17, 19, 21] in this area has focused on developing non-volatile memory programming libraries (NVMPLs) which enable programmers to specify a failure-atomic section (FASE) of updates to persistent data using familiar programming languages such as C/C++. One such NVMPL Atlas automatically infers such a FASE from legacy lock-based code. All of NVMPLs mentioned above, including Atlas, use persistent transactional logs to enforce failure atomicity. The major drawback of this approach is the high cost of writing and flushing logs synchronously to NVRAM. Furthermore, automatic or manual code changes are necessary to generate such logs. On the other hand, copy-on-write approach to updating data is inherently failure atomic without additional code changes. Furthermore, it does not require expensive logging. The advantage of the log-based approach is the ability to easily add atomicity to an arbitrary set of writes at an arbitrary granularity. This chapter of the thesis work demonstrates how the log-based transactional approach can be combined with copy-on-write to achieve the best of both worlds.

### 4.2 Lack of NVRAM Applications

previous work has suffered from the lack of benchmarks and real-world data structures that are cognizant of NVRAM. This chapter also addresses this problem by developing an NVRAM version of the commercially used legacy disk-based key-value store. This chapter describes MDB-NVM, which is an NVRAM-based key-value store implemented using C programming language. This key-value store preserves the API and the functionality of MDB [26] such that it could be used instead of MDB-NVM out of the box. MDB is a disk-based key-value store that is designed to replace BerkeleyDB [27] in a commercial and non-commercial setting as an improved backend for OpenLDAP. MDB-NVM is implemented partially using Atlas NVMPL [19] and copy-on-write mechanism for consistency. MDB-NVM played a crucial role in the development and evaluation of Atlas.

### 4.3 Contributions

This work makes the following contributions:

- 1. demonstrated how copy-on-write can be combined with a lock-based transactional approach to improve programmability and lower persistence overhead.

- 2. developed a real-world data structure that is designed to utilize NVRAM,

- a measurement of the cost of persisting a real-world data structures under workloads with varying characteristics.

### 4.4 Atlas Programming Library

Altlas Library adds durability semantics to the lock-based concurrent programs, typically with very little effort from a programmer [19]. In programs written using locks, shared data structures are modified only within a critical section, marked by lock acquire and release, to avoid data races and guarantee their consistency. Hence, Atlas assumes that these data structures only become inconsistent within critical sections and are consistent everywhere else. This assumption fails in cases of single-threaded programs, data structures that are isolated by design, or when a programmer writes non-blocking multithreaded code using primitives such as compare-and-swap. In such cases, a programmer can specify the section of code that requires atomicity w.r.t failure using programming construct nvm\_begin\_durable and a matching nvm\_end\_durable. Note that this construct does not guarantee thread-safety.

#### 4.4.1 Failure Atomic Section and Consistency Guarantees

Locks can be acquired and released in a nested pattern. Data cannot be considered consistent when any of the locks are held. Therefore, the whole outermost critical section in a given thread has to be executed atomically w.r.t failure. This outermost critical section executed by a thread is called the Failure Atomic SEction (FASE). FASEs between two threads may establish a happen before relationship during the runtime through lock acquire and release. Note that the start and the end of the outermost critical section may not be marked by the acquire and the release of the same lock, due to cases such as hand-over-hand locking.

In Atlas, an execution of a FASE becomes durable (i.e. visible in NVRAMeven after a restart) only if all updates to persistent memory made within that phase are durable. This guarantees an all-or-nothing behavior of a FASE w.r.t failure. Furthermore, given FASEs  $f_1$  and  $f_2$  such that  $f_1$  is sequenced before  $f_2$  as established by lock acquire and release, the  $f_2$  is durable only if  $f_1$  is so. Lastly, Atlas ensures that if a FASE is made durable, all updates to persistent memory that are sequenced before the FASE as established by runtime happen-before relationships are also durable. These requirements enforced by Atlas library maintains the consistency of persistent data structure stored in NVRAM across failures and restarts. After failure or restart, the persistent data is in the state as though each thread stopped execution at some program point where no locks were being held.

#### 4.4.2 Compiler Instrumentation and Runtime

Hidden from a programmer, Atlas uses a combination of write-ahead logs with undo information, cache line flushes and memory fences to ensure correct visibility ordering of updates to persistent memory and to enforce failure atomicity. A compilation pass instruments synchronization operations and store operations that appear directed to persistent memory. During the runtime, the instrumented stores call the Atlas runtime library which may create persistent logs, execute memory visibility barriers comprising of memory fences and cache line flushes. Atlas keeps the log structure and the log entries themselves consistent across failures. These log entries contain sufficient information to recreate a consistent state after a failure or a restart.

Atlas makes log entries with undo information visible in persistent memory before stores to the corresponding locations become visible. This enables Atlas recovery to replay the log entries to undo the effect of any stores that are not part of the last consistent state achieved. Furthermore, each log entry becomes visible in NVRAM atomically and in program order.

**Consistent State Computation** A helper, separate from the worker thread computes a consistent state from the persistent log, advances the persistent data structure's consistent state, and removes the log entries associated with the latest consistent state achieved. To advance the consistent state, a helper thread creates a graph where each node corresponds to a set of log entries associated with each FASE executed by each worker thread. The ordered edges representing the happens-before relationship may join one or more nodes in the graph. First Atlas marks all nodes in this graph representing FASEs as durable. Then it marks FASEs with unmatched acquire(s) and release(s) in the FASE as incomplete and hence non-durable. Furthermore, all nodes reachable from incomplete nodes are also marked as non-durable. The effects of non-durable FASEs are not to be seen by user code after a failure or a restart and are not part of the newly computed consistent state. Therefore, undo information related to incomplete nodes are preserved to undo the memory effect in the case of a crash or restart. The rest of the log entries associated with complete nodes unreachable from any incomplete nodes are purged.

#### 4.4.3 Failure, Restart, and Recovery

Under the persist-reuse model, Atlas follows, a programmer adds code that checks for the prior version of the data available upon restart (both normal and post-failure). If the prior version of the data is available, this "restart code", adjusts the programming context so as to resume the computation from this data.

In the case of a failure (e.g. sudden power loss), persistent data may not be in a consistent state. This inconsistent state is never visible to the application. Upon restart, Atlas first computes a consistent state from the persistent logs and prunes the log as helper thread may have lagged behind before the failure. Next, it replays the outstanding logs (after pruning) associated with incomplete FASEs and un-does any inconsistent updates

restoring the data structure to a consistent state. Once the persistent data is restored to a consistent state, user applications may resume.

### 4.5 MDB-NVM: NVRAM Key-value Store

MDB-NVM stores data in persistent memory and ensures that it is always consistent. It is thread-safe and uses a copy-on-write mechanism to avoid conflicts between read and write transactions. Therefore, multiple read transactions can proceed alongside the write transaction. MDB-NVM only supports one active write transaction at a time.

#### 4.5.1 **Programming Interface**

Figure 4.1 lists the common method calls to interact with MDB-NVM. These interfaces are similar to ones provided by MDB.

**Initialization, Setup, and Shutdown API:** mdb\_nvm\_env\_create (line 1) creates an environment object and stores in the location pointed by its argument. A MDB\_env object holds contains several fields to hold information about the MDB database such as the size of the NVRAM region to be allocated for this database etc. An NVRAM persistent region is a named container, similar to a mmap-ed file, that stores persistent data [19].

mdb\_nvm\_env\_open (line 2) takes the MDB\_env object, created by the call to line 1, as an argument, initializes MDB-NVM and populates the argument object with current MDB-NVM settings. The three arguments path, flags, and mode are not necessary and are only preserved for compatibility with MDB. mdb\_nvm\_txn\_begin (line 3) creates a transaction to be used with the given environment. The parent argument is for a nested transaction which is not currently supported in MDB-NVM, and as a result NULL can be passed as the argument. The flag argument indicates whether the transaction is read-only or read-write.

mdb\_nvm\_dbi\_open (line 4) opens a database referred by the name in the given environment. If the name argument is null, it opens the default database. MDB-NVM currently only supports a single default database, and hence the name argument is ignored. MDB-NVM

```

1: int mdb nvm env create (MDB env ** env)

2: int mdb nvm env open (MDB env * env, const char *path,

unsigned int flags, mdb mode t mode)

3: int mdb nvm txn begin (MDB env *env, MDB txn *parent,

unsigned int flags, MDB txn **txn)

4: int mdb nvm dbi open (MDB txn *txn, const char *name,

unsigned int flags, MDB dbi *dbi)

5: int mdb nvm txn commit (MDB txn *txn)

6: void mdb nvm txn abort (MDB txn *txn)

7: void mdb nvm dbi close (MDB env *env, MDB dbi dbi)

8: void mdb nvm env close(MDB env *env)

9: int mdb nvm put (MDB txn *txn, MDB dbi dbi,

MDB val *key, MDB val *data, unsigned int flags)

10:int mdb_nvm_get(MDB_txn *txn, MDB_dbi dbi,

MDB val *key, MDB val *data)

11:int mdb nvm cursor open (MDB txn *txn, MDB dbi dbi,

MDB cursor **cursor)

12:int mdb nvm cursor get(MDB cursor * cursor,MDB val *key,

MDB val *data, MDB cursor op op)

13:void mdb nvm cursor close (MDB cursor *cursor)

14:int mdb nvm del (MDB txn *txn, MDB dbi dbi,

MDB val *key, MDB val *data)

. . .

```

Figure 4.1: A non-exhaustive list of MDB-NVM API. A complete list can be found in mdb.h

returns the database handler object by storing it in at the address provided as the  $4^{th}$  argument dbi.

mdb\_nvm\_txn\_commit (line 5) commits the given transaction whereas mdb\_nvm\_txn\_abort (line 6) aborts the transaction. A read-only transaction can be aborted with no effect to the database as such a transaction does not modify the database.

mdb\_nvm\_dbi\_close and nvm\_env\_close closes the database handle and destroys the environment object created respectively. Both of these calls should only be used at the end to cleanly shutdown the database. They should also only be called once by a single thread.

**Read and Write API:** mdb\_nvm\_put (line 9) stores a <key, data> pair into the database indicated by the MDB\_dbi database handler object (returned by line 4). Note that there is only one default database supported in MDB-NVM at the moment. The key and data both have to be of type MDB\_val, which has the following structure:

```

typedef struct MDB_val {

/**< size of the data item */

size_t mv_size;

/**< pointer to the data item */

void *mv_data;</pre>

```

```

} MDB_val;

```

mdb\_nvm\_get returns the value and the size of the data associated with the *key* argument if it exists in the database. It returns the value (of type MDB\_val) by assigning its address to the field mv\_data in the 4<sup>th</sup> argument data. The address of the data belongs to MDB-NVM and therefore, the user application should make a copy instead of directly modifying it.

mdb\_nvm\_cursor\_open (line 11) creates a cursor capable of traversing the entire

database. It returns the cursor handle by storing the address of the handle in the cursor

(3<sup>rd</sup>) argument. mdb\_nvm\_cursor\_get (line 12) returns the <key, value> pair at the current

cursor position. The 4<sup>th</sup> argument op instructs MDB-NVM on the next position of the cursor. mdb\_nvm\_cursor\_close (line 13) destroys the cursor handle.

Finally, mdb\_nvm\_del (line 14) deletes the <key,value> pair matching the given key from the database if it exists. This operation requires the transaction to be opened in the read-write mode just like the put operation. Figure 4.2

## 4.5.2 Internal Structure

MDB-NVM is thread-safe, and failure-safe. MDB-NVM stores user data in persistent memory maintain its consistency. It maintains only the essential metadata about the database in persistent memory to minimize the cost of persistence. Rest of the metadata is recreated from the persistent metadata and maintained in transient memory. We discuss and distinguish below transient vs. persistent metadata:

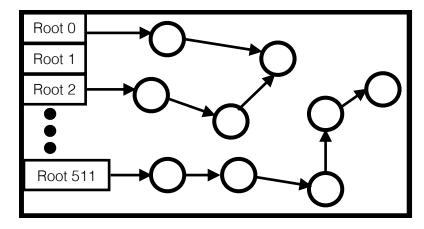

#### **Persistent B-tree**