**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

# RICE UNIVERSITY

# Compiler Support for Software Prefetching

by

### Nathaniel McIntosh

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

## **Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Ken Kennedy, Noah Harding Professor Department of Computer Science

Rice University

Keith Cooper, Associate Professor Department of Computer Science

Rice University

Sarita Adve, Assistant Professor

Department of Electrical and Computer

Engineering

Rice University

Houston, Texas

May, 1998

UMI Number: 9827422

UMI Microform 9827422 Copyright 1998, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

# Compiler Support for Software Prefetching

### Nathaniel McIntosh

#### Abstract

Due to the growing disparity between processor speed and main memory speed, techniques that improve cache utilization and hide memory latency are often needed to help applications achieve peak performance. Compiler-directed software prefetching is a hybrid software/hardware strategy that addresses this need. In this form of prefetching, the compiler inserts cache *prefetch* instructions into a program during the compilation process. During the program's execution, the hardware executes the prefetch instructions in parallel with other operations, bringing data items into the cache prior to the point where they are actually used, eliminating processor stalls due to cache misses.

In this dissertation, we focus on the compiler's role in software prefetching. In a set of experimental studies, we evaluate the performance of current software prefetching strategies, first for sequential benchmark programs running on a simulated uniprocessor machine, and then for a set of parallel benchmarks on a simulated distributed shared memory (DSM) multiprocessor. In these experiments, we employ a variety of enhanced efficiency metrics that allow us to focus on the compiler-related aspects of software prefetching. Based on the results of our experiments, we propose and experimentally evaluate a series of new compiler techniques for software prefetching. Our contributions include more powerful forms of compile-time reuse analysis, to reduce the frequency of useless prefetches, and new strategies for scheduling prefetches that reduce penalties incurred due to late prefetches. In the area of prefetching for DSM multiprocessors, we present a novel data-flow framework for analyzing communication patterns within parallel programs. We show how a compiler can use the information generated by this framework to provide better prefetching for long-latency coherence misses.

# Acknowledgments

I would like to acknowledge the generous support of DARPA, the NSF, and IBM Corporation, whose financial assistance made my graduate studies possible. In addition, I would like to particularly thank the following people:

- my thesis committee, Ken Kennedy, Keith Cooper, and Sarita Adve, for their constant support for my research efforts

- Kathi Fletcher, for making her simulator available for my experiments

- Paul Havlak, for developing the CFG, SSA, and Value Numbering packages in the D system software

- Seema Hiranandani, for helping me obtain a collection of compiler-parallelized benchmark programs

- Kathi Fisler and Moshe Vardi, for unselfishly donating CPU cycles on their UltraSparc machine for overnight simulations

- my fellow students Kathryn McKinley, Chau-Wen Tseng, Jerry Roth, Taylor Simpson, Nenad Nedeljković, Dejan Mirčevski, Phil Schielke, and others, for their inspiration, help, and advice along the way

- Don Baker, Tasshi Dennis, Reinhard von Hanxleden, and Mike Paleczny, my bicycling partners, for accompanying me on countless grueling 7:30 AM rides

- Amy Pullen, my wife, for her patience and encouragement during my many years of graduate study

My thanks to all the people above, and many others, for making my time at Rice a productive and enjoyable one.

# Contents

|   | Abs           | stract   |                                                  | i   |

|---|---------------|----------|--------------------------------------------------|-----|

|   | Ack           | nowled   | gments                                           | ii  |

|   | List          | of Illus | strations                                        | vii |

| 1 | Int           | rodu     | ction                                            | 1   |

| 2 | $\mathbf{Re}$ | lated    | Work                                             | 4   |

|   | 2.1           | Cache    | e design                                         | 2   |

|   | 2.2           | Prior    | work on software prefetching                     | 6   |

|   |               | 2.2.1    | Uniprocessor architectures                       | 6   |

|   |               | 2.2.2    | Multiprocessor architectures                     | 8   |

|   |               | 2.2.3    | Mowry, Lam, and Gupta's prefetching algorithms   | 10  |

|   | 2.3           | Relate   | ed areas                                         | 12  |

|   |               | 2.3.1    | Hardware prefetching                             | 13  |

|   |               | 2.3.2    | Comparisons of hardware and software prefetching | 15  |

|   |               | 2.3.3    | Multi-threaded architectures                     | 16  |

|   |               | 2.3.4    | Instruction scheduling                           | 17  |

|   |               | 2.3.5    | Compiler management of cache                     | 17  |

|   | 2.4           | Summ     | nary                                             | 18  |

| 3 | Co            | mpile    | r Overview                                       | 19  |

|   | 3.1           | -        | ch implementation                                | 19  |

|   |               | 3.1.1    | A researcher's dilemma                           | 19  |

|   |               | 3.1.2    | Shadow array implementation of prefetches        | 20  |

|   |               | 3.1.3    | Shadow regions for Fortran programs              | 21  |

|   |               | 3.1.4    | Tradeoffs involved in the use of shadow arrays   | 22  |

|   | 3.2           | Compi    | ilation stages                                   | 23  |

|   | 3.3           |          | analysis and transformation                      | 23  |

|   |               | 3.3.1    | Target loop selection                            | 23  |

|   |     | 3.3.2  | Reuse analysis                                     | 25 |

|---|-----|--------|----------------------------------------------------|----|

|   |     | 3.3.3  | Loop peeling analysis                              | 27 |

|   |     | 3.3.4  | Prefetch distance calculation                      | 27 |

|   |     | 3.3.5  | Transformation ordering                            | 28 |

|   |     | 3.3.6  | Source code size                                   | 28 |

|   | 3.4 | New t  | echniques                                          | 28 |

|   |     | 3.4.1  | Enhanced loop peeling                              | 30 |

|   |     | 3.4.2  | Loop strip-mining to reduce code expansion         | 33 |

|   |     | 3.4.3  | Cross-loop reuse analysis for prefetching          | 35 |

|   |     | 3.4.4  | Prolog overlap                                     | 36 |

|   |     | 3.4.5  | Outer loop pipelining                              | 38 |

|   | 3.5 | Summ   | nary                                               | 40 |

| 4 | Eva | aluati | ng software prefetching                            | 41 |

|   | 4.1 |        | uction                                             | 41 |

|   | 4.2 |        | ch target selection                                | 42 |

|   |     | 4.2.1  | Coverage                                           | 43 |

|   |     | 4.2.2  | Overshoot                                          | 44 |

|   |     | 4.2.3  | Selectivity                                        | 45 |

|   | 4.3 | Overh  | ead                                                | 45 |

|   | 4.4 |        | ıling                                              | 46 |

|   | 4.5 |        | ne characteristics                                 | 48 |

|   | 4.6 | Summ   | ary                                                | 50 |

| 5 | Un  | iproce | essor Prefetching                                  | 51 |

|   | 5.1 | _      | ocessor benchmark programs                         |    |

|   | 5.2 |        | tor                                                | 52 |

|   | 5.3 |        | ler parameters                                     | 53 |

|   | 5.4 |        | ion time                                           | 54 |

|   | 5.5 |        | mental data on prefetching performance             | 55 |

|   |     | 5.5.1  | Prefetch target selection                          | 55 |

|   |     | 5.5.2  | Instruction overhead                               | 63 |

|   |     | 5.5.3  | Experimental data on prefetch scheduling           | 66 |

|   | 5.6 | New u  | niprocessor compiler techniques                    | 68 |

|   |     | 5.6.1  | Techniques for improving prefetch target selection | 69 |

|   |     |        |                                                    |    |

|   |     | 5.6.2                | Techniques related to instruction overhead        | 72  |

|---|-----|----------------------|---------------------------------------------------|-----|

|   |     | 5.6.3                | Applying strip-mining to moderate loop unrolling  | 72  |

|   |     | 5.6.4                | Techniques to improve prefetch scheduling         | 75  |

|   | 5.7 | Sumn                 | nary                                              | 78  |

| _ |     | _                    |                                                   |     |

| 6 |     |                      | op Reuse Analysis and Transformations             | 80  |

|   | 6.1 |                      | duction                                           | 80  |

|   | 6.2 |                      | sis framework                                     | 81  |

|   |     | 6.2.1                | Control flow representation                       | 82  |

|   |     | 6.2.2                | Data-flow universe                                | 84  |

|   |     | 6.2.3                | Initial information                               | 85  |

|   |     | 6.2.4                | Reuse equations                                   | 85  |

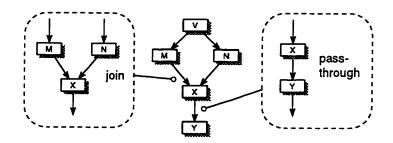

|   |     | 6.2.5                | Meet $(\bigwedge)$ and join $(\bigvee)$ operators | 86  |

|   |     | 6.2.6                | Incorporating cache constraints                   | 87  |

|   |     | 6.2.7                | Complexity                                        | 90  |

|   |     | 6.2.8                | Interprocedural analysis                          | 91  |

|   | 6.3 | Applio               | cations of cross-loop reuse information           | 91  |

|   |     | 6.3.1                | Elimination of useless prefetches                 | 91  |

|   |     | 6.3.2                | Locality-enhancing loop transformations           | 92  |

|   |     | 6.3.3                | Transformation selection                          | 93  |

|   | 6.4 | Experimental results |                                                   |     |

|   |     | 6.4.1                | Compilation                                       | 94  |

|   |     | 6.4.2                | Simulator                                         | 94  |

|   |     | 6.4.3                | Benchmark programs                                | 95  |

|   |     | 6.4.4                | Results                                           | 95  |

|   | 6.5 | Relate               | ed work                                           | 98  |

|   | 6.6 | Summ                 | ary                                               | 100 |

| _ |     |                      |                                                   |     |

| 7 |     |                      | •                                                 | 102 |

|   | 7.1 |                      | uction                                            | 102 |

|   | 7.2 |                      | multiprocessors                                   | 104 |

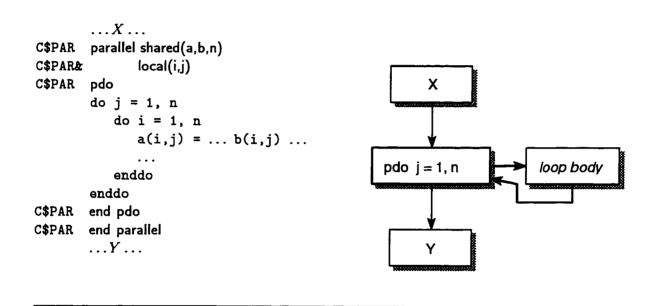

|   | 7.3 | Paralle              | el program model                                  | 105 |

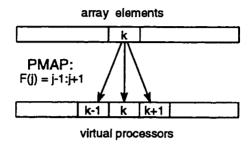

|   |     | 7.3.1                | Parallel code generation                          | 106 |

|   | 7.4 | Evalua               | ation of software prefetching for DSM machines    | 106 |

|   |     | 7.4.1                | Parallel benchmark programs                       | 108 |

|              |     | 7.4.2  | Parallel coverage                          | . 109 |

|--------------|-----|--------|--------------------------------------------|-------|

|              |     | 7.4.3  | Architectural parameters                   | . 110 |

|              |     | 7.4.4  | Compiler parameters                        | . 111 |

|              |     | 7.4.5  | Performance of prefetching on DSM machines | . 112 |

|              |     | 7.4.6  | Outcomes for prefetches                    | . 113 |

|              |     | 7.4.7  | Prefetch scheduling: a closer look         | . 114 |

|              | 7.5 | Comp   | oiler framework                            | . 115 |

|              |     | 7.5.1  | Predicting coherence misses: an overview   | . 115 |

|              |     | 7.5.2  | Array-section analysis                     | . 116 |

|              |     | 7.5.3  | Predicting coherence misses                | . 118 |

|              |     | 7.5.4  | Interval analysis                          | . 123 |

|              |     | 7.5.5  | Data-flow equations                        | . 124 |

|              |     | 7.5.6  | Incorporating cache size constraints       | . 128 |

|              | 7.6 | Optin  | nizations                                  | . 130 |

|              |     | 7.6.1  | Exploiting coherence miss information      | 133   |

|              |     | 7.6.2  | Additional optimizations                   | 134   |

|              | 7.7 | Exper  | operiments                                 |       |

|              |     | 7.7.1  | Subroutines                                | 137   |

|              |     | 7.7.2  | Optimizations                              | 137   |

|              | 7.8 | Summ   | nary                                       | 140   |

| 8            | Co  | nclusi | ions                                       | 141   |

|              | Bib | liogra | aphy                                       | 143   |

| $\mathbf{A}$ | Int | erpro  | cedural analysis to support shadow regions | 153   |

| В            | Cad | che vo | olume estimation for nested loops          | 155   |

# Illustrations

| Prefetch pipelining                                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

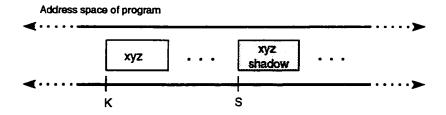

| Implementing prefetches with shadow regions                  | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Shadow array prefetching example                             | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Compilation stages                                           | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Analysis stages for inner loops                              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Analysis stages for non-inner loops                          | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Transformation overview                                      | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Compiler source code size                                    | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Reuse analysis for imperfectly nested loops                  | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Section-based group temporal dependence check                | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Strip-mining in combination with unrolling                   | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Example of cross-loop reuse                                  | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Prolog overlap                                               | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Outer loop pipelining                                        | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Outer loop pipelining with strip-mining                      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Prefetching efficiency metrics                               | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Control flow within an inner loop                            | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                              | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Prefetch scheduling                                          | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

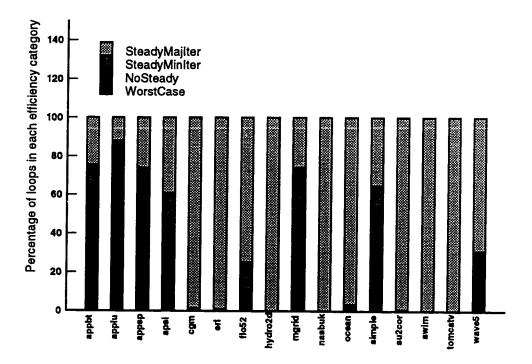

| Pipeline efficiency categories                               | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Uniprocessor benchmark programs and their vital statistics   | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Architectural parameters for uniprocessor simulations        | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Execution time reduction due to prefetching, 1 processor     | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Prefetch coverage factors                                    | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Reference categories by lexical/interprocedural loop nesting | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                              | Implementing prefetches with shadow regions Shadow array prefetching example. Compilation stages Analysis stages for inner loops Analysis stages for non-inner loops Transformation overview Compiler source code size Reuse analysis for imperfectly nested loops Section-based group temporal dependence check Strip-mining in combination with unrolling Example of cross-loop reuse Prolog overlap Outer loop pipelining Outer loop pipelining with strip-mining  Prefetching efficiency metrics Control flow within an inner loop Instruction overhead Prefetch scheduling Pipeline efficiency categories  Uniprocessor benchmark programs and their vital statistics Architectural parameters for uniprocessor simulations Execution time reduction due to prefetching, 1 processor Prefetch coverage factors |

| 5.6  | Loop nesting breakdown for uncovered cache misses                          | 57 |

|------|----------------------------------------------------------------------------|----|

| 5.7  | Useless prefetches as a total of all prefetches                            | 59 |

| 5.8  | Inner and outer loop epochs                                                | 59 |

| 5.9  | Epoch values stored with each cache line                                   | 60 |

| 5.10 | Categories of useless prefetches                                           | 61 |

| 5.11 | Useless prefetch breakdown                                                 | 61 |

| 5.12 | Overshoot and Virtual Overshoot                                            | 62 |

| 5.13 | Instruction overhead from prefetching                                      | 64 |

| 5.14 | Effect of cache line size on IPP                                           | 65 |

| 5.15 | Pipeline efficiency metrics                                                | 67 |

| 5.16 | Late prefetches as a percentage of useful prefetches                       | 68 |

| 5.17 | Spectrum of reuse analysis techniques                                      | 69 |

| 5.18 | Effects of more general reuse analysis methods                             | 70 |

| 5.19 | Group-spatial reuse among irregular references                             | 71 |

| 5.20 | Effects of group-spatial reuse analysis on selected irregular applications | 72 |

| 5.21 | Compile time and executable size increase with longer cache lines          | 73 |

| 5.22 | Compile time and executable size increase, with strip-mining               | 74 |

| 5.23 | Applicability of scheduling optimizations                                  | 75 |

| 5.24 | Effects of prolog overlap on performance                                   | 76 |

| 5.25 | Effects of outer loop pipelining on performance                            | 77 |

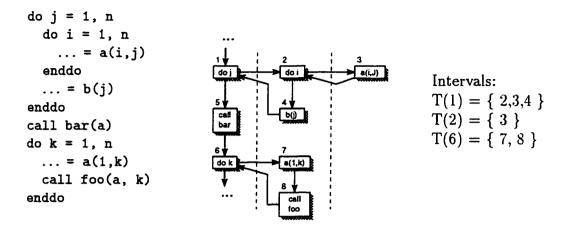

| 6.1  | Example sub-program with interval-flow graph                               | 83 |

| 6.2  | Reuse equations                                                            | 85 |

| 6.3  | Procedure for computing reuse equations                                    | 86 |

| 6.4  | Control flow                                                               | 87 |

| 6.5  | V for finite cache case                                                    | 89 |

| 6.6  | Compilation stages                                                         | 94 |

| 6.7  | Program characteristics                                                    | 96 |

| 6.8  | Simulation data for original programs [thousands]                          | 96 |

| 6.9  | Transformation summary                                                     | 96 |

| 6.10 | Simulation data for transformed programs [thousands]                       | 97 |

| 6.11 | Percent change between original and transformed (no profile data)          | 97 |

|      | Transformation summary (with profile)                                      | 99 |

|      | Simulation data for transformed programs, with profile [thousands] .       | 99 |

| 6.14 | Percent change between original and transformed (with profile)        | 99  |

|------|-----------------------------------------------------------------------|-----|

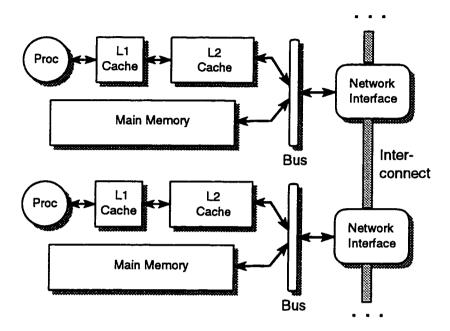

| 7.1  | DSM multiprocessor block diagram                                      | 103 |

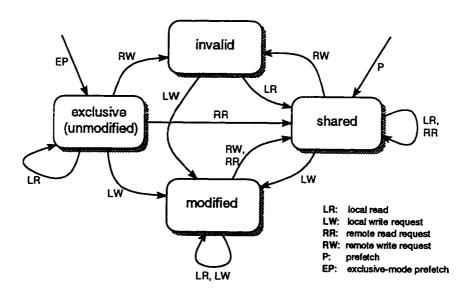

| 7.2  | State diagram for example MESI cache coherence protocol               | 104 |

| 7.3  | Parallelization directives                                            | 107 |

| 7.4  | Parallel program excerpt                                              | 108 |

| 7.5  | Miss rates for parallelized benchmarks                                | 109 |

| 7.6  | Parallel coverage                                                     | 110 |

| 7.7  | Network parameters for DSM multiprocessor simulations                 | 111 |

| 7.8  | Execution time reduction due to prefetching, 4 processors             | 112 |

| 7.9  | Outcome breakdown for prefetches, 4 processors                        | 113 |

| 7.10 | Late prefetches as a percentage of useful prefetches, 4 processors    | 114 |

| 7.11 | Example loop nests with section information                           | 117 |

| 7.12 | Parallel loop with corresponding CFG                                  | 119 |

| 7.13 | Possible outcomes for a cache-coherent read (worst-case)              | 121 |

| 7.14 | Conditions for predicting read outcomes                               | 121 |

| 7.15 | Possible outcomes of cache-coherent write (worst-case)                | 122 |

| 7.16 | Conditions for predicting write outcomes                              | 122 |

| 7.17 | Data-flow sets                                                        | 125 |

| 7.18 | Data-flow equations computed within an interval                       | 126 |

| 7.19 | Data-flow equations for interval summarization                        | 127 |

| 7.20 | Read outcomes based on data-flow sets                                 | 128 |

| 7.21 | Write outcomes based on data-flow sets                                | 128 |

| 7.22 | Data-flow equations computed within an interval (with cache           |     |

|      | constraints)                                                          | 129 |

| 7.23 | Interval summarization equations (with cache constraints)             | 130 |

| 7.24 | Example with coherence misses                                         | 131 |

| 7.25 | Example with many-processor read-sharing                              | 132 |

| 7.26 | Example with false sharing                                            | 132 |

| 7.27 | Exclusive-mode prefetching opportunities                              | 135 |

| 7.28 | Selected subroutines                                                  | 137 |

| 7.29 | Optimization strategies                                               | 138 |

| 7.30 | Relative performance of different optimization strategies             | 139 |

| 7.31 | Percent reduction in late prefetch penalty, increase in overshoot for |     |

|      | each optimization strategy                                            | 139 |

|   | ۰ |

|---|---|

| v |   |

| А | L |

|   |   |

| A.1  | Algorithm | for computing ShadowForFormal      | 154     |

|------|-----------|------------------------------------|---------|

| 41.1 | Migorithm | tor combaning suggestion comparing | <br>LOT |

# Chapter 1

### Introduction

One of the major challenges that computer architects have faced during recent years is the widening gap between processor speed and main memory latency. The rate at which processors execute computations has grown much more quickly than the speed with which items can be fetched from memory. Cache memories are the primary tool that designers use to cope with this mismatch. As a result, cache design has been intensively researched in recent years, and cache hit rates are now a critical component of overall program performance. Cache memories are not perfect, however. In order to effectively exploit the cache, a program has to exhibit locality of reference, and even programs with good locality must incur cache misses now and then. For this reason, techniques that improve cache utilization and hide the latency of cache misses are very important.

This dissertation concentrates on a particular latency hiding technique: compiler-directed software prefetching. In this form of prefetching, the compiler inserts non-binding cache prefetch instructions into a program as it is being compiled. At runtime, the program issues prefetch operations to fetch data items into the cache before they are explicitly loaded, effectively hiding the latency that would ordinarily be incurred due to cache misses.

Previous researchers have established software prefetching as a viable method for improving cache hit rates. This research has explored the architectural issues surrounding prefetching in considerable detail. In our work we choose to focus on the compiler-related aspects of software prefetching. Our goal is to advance the state of the art with respect to compiler design in this area, and to provide useful information to future compiler designers.

The chief contributions in this thesis are as follows. First, we perform detailed performance evaluations of software prefetching for both sequential and parallel programs. Throughout these evaluations, our emphasis is on gauging the efficiency of the compiler algorithms employed. Based on the data from our evaluations, we propose a series of new compiler techniques for software prefetching.

For uniprocessor architectures, our contributions are in two main areas: new methods for detecting and eliminating useless prefetches, and new techniques for improving prefetch scheduling. We develop a pair of reuse analysis strategies that are more powerful than those applied in previous work, and we experimentally evaluate their effectiveness. Our results show that our more general methods are useful primarily for programs that make extensive use of imperfect loop nests, which are more difficult to analyze than perfect loop nests. In the area of prefetch scheduling, our new optimizations are effective in reducing late prefetch penalties. Performance improvements due to scheduling optimizations are fairly modest, however, since relatively few programs incur significant numbers of late prefetches on our simulated uniprocessor.

For multiprocessor architectures, we focus on the issues surrounding software prefetching for parallel programs running on distributed shared-memory (DSM) machines. These architectures present a series of additional challenges to the compiler, due to their increased overall memory latency and their more variable cache miss latencies. The results from our experimental study of compiler-parallelized benchmark programs running on a simulated DSM show that late prefetches are a much more serious problem than in case of uniprocessor architectures. To address this problem, we develop a new form of compiler analysis designed to predict the loops and references that cause coherence activity within a parallel program. We show how our compiler can use the information gathered by this analysis to provide better prefetch scheduling, and we present a set of partial experimental results that demonstrate the effectiveness of these techniques in practice.

The foundation for many of our analysis techniques is a new compiler framework for detecting cross-loop reuse: repeated data accesses that take place between loop nests, as opposed to within a single loop nest. This framework incorporates both data-flow analysis, to handle intra-procedural control flow, and array-section analysis, to compactly summarize regions of arrays accessed within loops. The information generated by the framework is useful for a variety of compiler tasks, including detecting and eliminating useless prefetches, and predicting the profitability of locality-enhancing loop transformations, such as loop fusion and loop reversal. Finally, it forms the basis of the analysis techniques we use for optimizing prefetching within parallel programs.

In order to support our experiments, we introduce a collection of enhanced metrics for characterizing and quantifying various aspects of prefetching performance. These metrics incorporate refinements designed to provide information on compiler behavior that is more useful than the data generated by existing methods.

Finally, we contribute a new approach to developing the compiler infrastructure needed to support research on software prefetching. By emulating prefetches using stores to compiler-generated "shadow regions", we avoid the prohibitively expensive step of developing an optimizing low-level compiler for the target architecture/instruction set. Our experiments demonstrate that using shadow arrays to emulate prefetches is a viable method for conducting research on software prefetching.

An outline of this dissertation is as follows. We begin in Chapter 2 by surveying the spectrum of latency-hiding techniques and other strategies with goals similar to those of software prefetching. We also summarize previous research on software prefetching, and highlight the unique contributions of our work relative to prior studies. Chapter 3 describes the internal architecture of our compiler, detailing the various analysis and transformation techniques we employ. In this chapter we also discuss the use of shadow arrays to implement prefetches. In Chapter 4, we present the system of efficiency metrics that we use to evaluate the performance of prefetching. Chapter 5 presents the results of our work on uniprocessor prefetching, including an experimental study of prefetching for a set benchmark programs running on a simulated uniprocessor architecture, and evaluations of our new uniprocessor compiler techniques. Chapter 6 describes our compiler framework for detecting cross-loop reuse. In Chapter 7 we address the problem of prefetching for DSM multiprocessors. We present our new compiler strategy for analyzing parallel programs, and we show how it can be used improve prefetching for this class of architectures. Finally, in Chapter 8 we summarize the contributions in this thesis and offer our concluding remarks.

# Chapter 2

### Related Work

In this chapter we summarize previous research on software prefetching, and we discuss other topics in the area of memory hierarchy management and memory latency hiding. An outline of this chapter is as follows. We begin in Section 2.1 by briefly discussing developments in cache design relevant to prefetching and to other latency-hiding techniques. In Section 2.2 we provide a survey of previous work on software prefetching, first for uniprocessor architectures and then for multiprocessors. Section 2.3 covers a variety of other hardware and software methods that hide memory latency and improve cache utilization. Section 2.4 contains a summary of our conclusions.

## 2.1 Cache design

The design of cache memories has been researched intensively over the last several decades [89]. We mention just a few of the important aspects of cache design that relate to software prefetching.

Multi-level cache hierarchies interpose multiple levels of cache between the processor and main memory. They provide a means of keeping overall miss penalties low without resorting to long cache hit latencies. Multi-level memory hierarchies typically enforce the *inclusion* principle, that is, the hardware requires that the contents of the cache at level K be a subset of the contents at K+1. The inclusion requirement is essential for efficient implementation of hardware cache coherence in multiprocessors [82]. In keeping with the widespread acceptance of multi-level hierarchies in modern workstation and multiprocessor designs, we assume a 2-level cache hierarchy for all of our simulation studies.

A write buffer is a small queue (2-32 entries) that stores pending write operations, typically placed between a cache and main memory or between two levels of cache in a multi-level hierarchy [89]. When a write is issued, the write buffer stores the written value and allows execution to resume before the write completes, thereby

masking the latency of the write. When combined with other architectural features such as a relaxed memory consistency model [1, 32] and a write-through primary cache, an aggressive write buffer will allow the compiler to issue prefetches only for load instructions, since most or all store latency will be hidden.

A lockup-free cache provides a mechanism for the processor to continue issuing instructions even after a cache miss, provided that the processor does not use the register that is the destination of the load instruction that caused the miss [58]. Software prefetching requires that the cache be lockup-free (at least with respect to prefetch operations), since prefetch operations must execute in parallel with other cache accesses in order to be effective. Lockup-free caches are often implemented through use of Miss Status Holding Registers (MSHR's), which keep information about pending requests. A lockup-free cache is typically more effective as a latency-hiding mechanism if it is combined with other advanced hardware features, such as multiple instruction issue [49], dynamic branch prediction [64], dynamic scheduling [33], register renaming [51], and/or speculative execution [77]. Although the latency-hiding mechanism provided by lockup-free caches is very general-purpose, it is limited by the amount of instruction-level parallelism in the program, as well as the ability of the processor to exploit that parallelism [7, 28].

We categorize cache misses using the following classification scheme [47]:

- a compulsory or cold start miss corresponds to the very first access to a given block of data made by a program, causing the block to be brought into cache

- capacity misses are due to situations where the cache is not large enough to hold all of the blocks referenced by the program, causing a given cache block to be evicted and then subsequently retrieved.

- conflict misses result when blocks are evicted from the cache due to limited associativity. Given an N-way set associative cache, if the program uses a group of K data items (K > N) that map to the same cache set, when one item from the group is brought into the cache, it will displace another item within the group, causing a miss when the evicted item is subsequently referenced.

- coherence misses occur on multiprocessors with invalidation-based cache coherence protocols. These misses take place when a given line in one processor's

<sup>&</sup>lt;sup>1</sup> Invalidation-based cache coherence protocols are discussed in Section 7.2.

cache is invalidated by a second processor, then subsequently referenced again by the first processor.

## 2.2 Prior work on software prefetching

In this section we give a summary of previous work on compiler-directed software prefetching, first for uniprocessors and then for multiprocessors. Our work differs from the studies mentioned below in three important respects. First, we provide an experimental infrastructure that is at least comprehensive and complete as those employed in prior studies (and in some cases more comprehensive). In particular, we apply prefetching to realistic-sized complete application programs (not kernels or individual loop nests), we provide a compiler implementation that integrates most of the techniques developed by previous researchers (as well as our own), and we use a very detailed simulator, capable of gathering useful statistics not available when running on real hardware. This combination allows us to provide new insights into the behavior of compiler-directed software prefetching. Second, our work is the first to apply reuse analysis techniques that look beyond the level of individual loop nests, gathering information about memory access patterns across an entire procedure or program. Finally, our compiler is the first to provide a comprehensive framework for analyzing the coherence patterns in a parallel program, allowing it to begin addressing some of the challenges that shared-memory multiprocessors present to software prefetching.

### 2.2.1 Uniprocessor architectures

Porterfield, Callahan, and Kennedy produced some of the first results on software prefetching [18, 79]. Their compiler targeted array accesses within loops, issuing prefetches for array data an iteration in advance. Since the simulator they used (PFCSim) operated at the level of subscripted array accesses and not instructions, it was difficult for them to accurately characterize instruction overhead and scheduling efficiency. Their work introduced the idea of an overflow iteration for predicting the cache behavior of loops.

Klaiber and Levy explored a form of software prefetching in which prefetched data are stored in a separate "fetch buffer", distinct from the cache [55]. They developed the idea of computing a prefetching distance for each loop, as a means of determining how far in advance to issue prefetches. The prefetching distance is calculated as  $\lceil \frac{C}{M} \rceil$ ,

where C is the number of instructions during a single iteration of the loop, and M is the expected memory latency in cycles. They did not implement a compiler as part of their work; for their experiments, they used the Livermore Loops [71], which they instrumented by hand with prefetch instructions.

Chen, Mahlke, Chang, and Hwu performed a series of studies that compared prefetching into a separate buffer with prefetching directly into cache [22]. They used trace-driven simulation to model a hypothetical multiple-issue processor equipped with support for software prefetching. Their simulation results indicated that prefetching into a separate prefetch buffer outperformed prefetching into the main cache in most cases. The use of a separate prefetch buffer for prefetching has seen little acceptance in commercial processor designs, however, most likely due to the additional cost and design complexity required.

Mowry, Lam, and Gupta provided a comprehensive study of software prefetching, for both uniprocessors and multiprocessors [73, 75]. In contrast to most previous implementations (in which prefetches were inserted into benchmark programs entirely by hand), they integrated their support for prefetching into an optimizing compiler for a MIPS-like architecture [92]. They simulated their compiled programs using a cycle-level simulator that modeled the cache and memory of the target machine in detail. To experimentally validate their techniques, they applied software prefetching to a set of kernels and small programs drawn from the SPEC, SPLASH, and NAS benchmark suites [10, 87, 96]. In addition to issuing prefetches for array references with affine subscript functions, their compiler also issued prefetches for references that used indirection arrays. They found that prefetching was quite effective for hiding memory latency; in most cases stalls due to memory latency were reduced by 50% or more. We discuss Mowry's work in more detail in Section 2.2.3.

Bernstein, Cohen, Freund, and Maydan described their compiler implementation of software prefetching for the PowerPC architecture, and provided performance results for the SPEC92fp benchmarks [14]. Their compiler strategy was similar in spirit to that of Mowry et al., although they targeted only references with affine subscript functions within inner loops. They were able to achieve performance improvements of (5-20%), which are significant given the relatively short memory latency (30 cycles) of the target architecture. They showed only total execution time improvement due to prefetching, since they did not employ simulation for their experiments.

Santhanam, Gornish, and Hsu evaluated the performance of software prefetching for the Hewlett Packard PA-8000 architecture [86]. In an experimental study, they

applied their compiler implementation of software prefetching to the programs in the the SPEC95fp benchmark suite, resulting in execution time improvements of up to 100%, with a harmonic mean value of 26%. They also included discussions of a variety of issues related to prefetching performance, including cache conflicts, memory bank conflicts, instruction overhead, and instruction scheduling. As with the work by Bernstein et al., the authors reported primarily execution times, as opposed statistics from simulations.

#### 2.2.2 Multiprocessor architectures

Gornish, Granston, and Veidenbaum implemented a form of software prefetching as part of their compiler for the Cedar machine, a shared-memory multiprocessor [36]. They focused on using prefetching to gather blocks of data into a processor's local memory, as opposed to into the cache. They employed sophisticated compiler analysis to handle the problem of determining the safety of accessing locally cached items, because their target architecture provided no support for keeping the contents of the local memories up to date with the contents of global memory. Since prefetched data were not at risk of being displaced (as is the case with prefetching into a cache), their compiler issued prefetch operations as early as possible. They observed that the additional traffic produced by prefetching sometimes caused delays for other memory operations.

Mowry and Gupta reported results on the effects of software prefetching for parallel programs running on the DASH shared-memory multiprocessor [74]. In this particular study, they inserted prefetch instructions by hand, instead of using a compiler. The goal of their work was to assess the effectiveness of software prefetching in reducing memory latency penalties for programs running on shared-memory multiprocessors with hardware cache coherence. They concluded that prefetching can indeed be beneficial, provided that there is enough memory bandwidth available.

In subsequent work, Mowry performed studies using a similar set of parallel programs (the SPLASH benchmarks [87]), but with a compiler implementation of software prefetching [73]. The compilation strategy used was similar to that used in the Mowry's uniprocessor experiments, but with the addition of exclusive-mode prefetching for write references (see Section 7.2 for a description of this enhancement). This work provided additional data on the overall effectiveness of prefetching and demon-

strated that exclusive-mode prefetching can be beneficial in terms of reducing network traffic on machines such as the DASH [65].

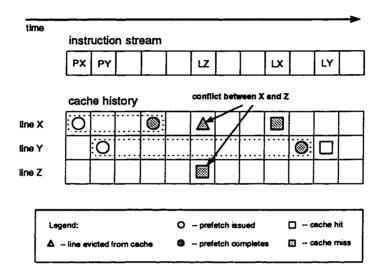

Tullsen and Eggers examined prefetching in the context of a bus-based, bandwidthlimited multiprocessor [94, 95]. Their study was based on off-line trace analysis, in which prefetch instructions were inserted into a previously generated program trace by consulting an "oracle". Their results were in three general areas. First, they found that for multiprocessors with very limited memory bandwidth, software prefetching will seldom produce any significant improvement, and can easily produce a degradation in performance. Second, they found that prefetching can exacerbate cache conflicts, but that the problems can often be overcome through the use of a victim cache [50]. Finally, they concluded that for the programs they considered, a significant fraction of the cache misses were due to coherence activity (i.e., invalidations), and that this source of misses should be considered in the prefetching strategy. There is some question as to whether results derived from oracle-inserted prefetch studies can be compared with studies in which a compiler is employed, however. The oracle used by Tullsen and Eggers was a simple uniprocessor cache simulator. The trace being studied was run through the cache simulator, and instructions that caused misses with the simple simulator were marked for prefetching during the multiprocessor simulation run. This method of inserting prefetches may generate prefetches that are substantially different from those generated by a compiler. For example, in the oracle method, prefetches are inserted for conflict misses, which are for all practical purposes undetectable at compile time (using existing techniques). Prefetching conflict misses may improve some programs, but it may make others worse, depending on the nature of the conflicts. Similarly, if cache miss behavior is very "bursty" during the oracle simulation, then prefetches will also be issued in a bursty fashion (which again may not necessarily the case when prefetches are inserted by compiler). In the absence of a comparative study, we are uncertain whether oracle prefetching studies provide reliable information to a compiler developer.

More recently, Ranganathan, Pai, Abdel-Shafi, and Adve examined the performance of software prefetching for a class of advanced multiple-issue shared-memory multiprocessor architectures [85]. Their simulator modeled a processor that is designed to take advantage of instruction-level parallelism (ILP). These processors exploit ILP by means of features such as dynamic instruction scheduling, branch prediction, and non-blocking reads, which overlap instructions and hide latency. The authors found that in spite of the processors' hardware-supported latency-hiding fea-

tures, programs still incurred significant memory latency penalties, and that software prefetching was found to be helpful in hiding this latency. The results also showed that prefetching placed additional strain on the processor's resources, creating significant problems in certain cases. The authors of this work inserted prefetch instructions into their benchmark programs by hand, simulating the various compiler techniques used by Mowry et al. Some of the optimizations they applied to improve performance were fairly aggressive; current-generation compilers would probably be unable to duplicate them automatically.

### 2.2.3 Mowry, Lam, and Gupta's prefetching algorithms

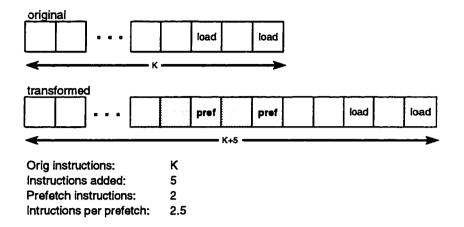

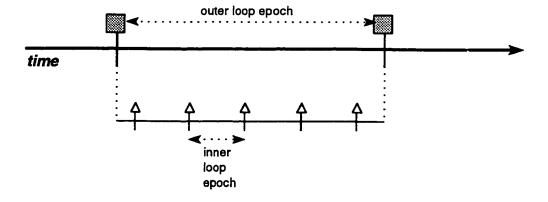

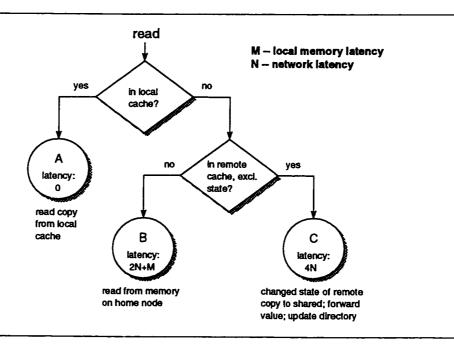

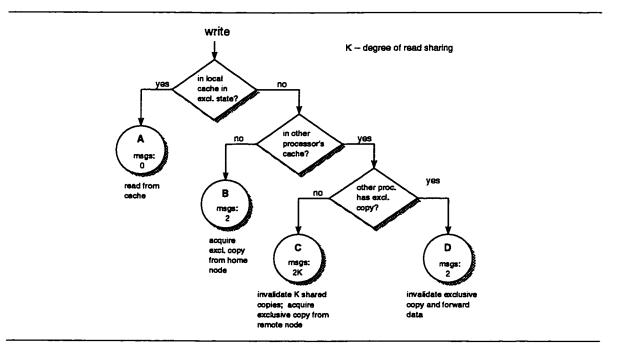

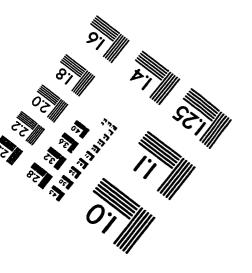

In this section we provide additional detail on some of the compiler techniques developed by Mowry, Lam and Gupta [75], since we have integrated many of them into our software prefetching scheme. The chief compiler-related contributions in the work of Mowry et al. are the use of locality analysis for selecting prefetch targets, software pipelining for effective scheduling of prefetches, and loop unrolling to reduce or eliminate the need for guarded prefetch instructions. The example in Figure 2.1 illustrates each of these steps. Part A of Figure 2.1 shows a loop nest containing references to an array. In this example, the cache line size is 16 bytes and each array element is 8 bytes long.

In part B of Figure 2.1, prefetch operations have been inserted and the loop has been split into three new loops. The first loop, the prolog, performs no computation but simply fetches data needed in the first few iterations of the original loop. Note that only a single prefetch is present for the array "a": the compiler's locality analysis has determined that the two references to "a" always access the same cache line (and thus only a single prefetch needs to be issued for the pair). The next loop, the steady-state, fetches data for later iterations while performing computation on array elements that have already been prefetched. The number of iterations in advance that items are fetched is known as the prefetching distance ("PD"), and in this example is equal to 8 iterations. The prefetching distance is calculated as  $\lceil \frac{C}{M} \rceil$ , where C is the number of instructions during a single iteration of the loop, and M is the expected memory latency in cycles. The third new loop is the epilog or cleanup; it executes the final iterations of the original loop without performing any prefetching. Initially, the prefetches in the prolog and steady-state are protected by guards to insure that they execute only on every other iteration (without the guards, two prefetches would be

```

A) Original loop nest

B) After prefetch pipelining

C) After loop unrolling

do i = 1, 1024

PD = 8

PD = 8

\cdots = x + a(i)

do i = 1, PD

do i = 1, PD, 2

\cdots = y + a(i)

if (i \mod 2 = 0)

prefetch a(i)

enddo

prefetch a(i)

enddo

endif

do i = 1, 1024-PD, 2

enddo

prefetch a(i+PD)

do i = 1, 1024-PD

\cdots = x + a(i)

if ((i+PD) \mod 2 = 0)

\cdots = y + a(i)

prefetch a(i+PD)

\cdots = x + a(i+1)

\cdots = y + a(i+1)

\cdots = x + a(i)

enddo

\cdots = y + a(i)

do i = 1024-PD+1, 1024

\cdots = x + a(i)

do i = 1024-PD+1, 1024

\cdots = y + a(i)

\cdots = x + a(i)

enddo

\cdots = y + a(i)

enddo

```

Figure 2.1 Prefetch pipelining

issued for each cache line, effectively wasting half the prefetches). In part C of Figure 2.1, the prolog and the steady-state loops have been unrolled, allowing each guarded prefetch to be replaced by a single unconditional prefetch. The unrolling factor is selected based on the minimum effective stride of the references in the loop; the compiler uses the smallest unrolling factor that will allow all prefetches to be issued unconditionally. In combination, these techniques schedule prefetches appropriately, avoid unnecessary prefetches, and avoid overhead due to guards.

In order to reduce the fraction of prefetches issued that are useless (i.e., those that hit in cache), Mowry uses temporal reuse analysis to recognize situations where a section S of a given array is repeatedly used within a given loop nest. It exploits this information by applying loop peeling, splitting a given loop nest into an initial "peel" loop (in which prefetches are issued for S), followed by the remainder of the loop (in which no prefetches are issued for S). Mowry's compiler also uses a form of multistage pipelining to support prefetching of references that access data through indirection arrays. This is accomplished by adding additional stages to the prefetch pipeline, to allow time to fetch the indirection array value before issuing the prefetch for the indirectly accessed location. For a single level of indirection, for example, the

first preloop stage prefetches the indirection array at distance 0, the second preloop stage prefetches the indirection array at distance D and the indirectly accessed data at distance 0, and then the steady state stage of the pipeline issues prefetches for both types of data, with indirection arrays prefetched at distance 2\*D and indirectly accessed data prefetched at distance D. See Mowry's thesis for the details [73].

Mowry's study was limited in certain ways, and we have tried to address some of these limitations in our work. First, some of the the programs he used were fairly small. In his uniprocessor studies, ten of thirteen uniprocessor benchmarks had 3 or fewer subroutines and were under 200 lines. Larger programs can often be difficult to analyze, and they tend to have more control flow and more procedure calls than kernels or small benchmarks. The benchmark programs used in our experiments are complete applications, and are of a size that is more representative of scientific and numerical programs used in practice.

Second, Mowry's compiler used only intra-loop reuse analysis, with an emphasis on perfectly nested loop nests. As part of this dissertation we develop more general intra-loop reuse analysis techniques, and we apply them to the problem of detecting useless prefetches. We also develop a framework for analyzing cross-loop reuse, that is, reuse of memory locations that takes place across outer loop nests. We provide experimental results on how useful these techniques are in practice.

Finally, Mowry's compiler targeted explicitly parallel programs when compiling for multiprocessors. Because of the nature of the application programs that he targeted, his compiler had no specific knowledge about communication patterns within the programs. It was therefore difficult for the compiler to target specific sets of references or loop iterations that incur long-latency cache misses. We address this limitation in our work through the development of a compiler framework for detecting and exploiting coherence activity in compiler-parallelized programs.

#### 2.3 Related areas

In this section we discuss various developments in compiler optimization and in computer architecture that are particularly relevant to software prefetching. Our goal is not to provide an exhaustive history of computer architecture and latency-hiding techniques, but rather to provide enough background material to allow the reader to understand the relative strengths and weaknesses of software prefetching compared to other methods.

In Section 2.3.1 we discuss hardware prefetching, and describe the advantages and disadvantages of hardware prefetching as compared to software prefetching. In Section 2.3.3 we discuss multithreaded architectures, which take an entirely different approach to memory latency hiding. Finally, we discuss a number of compiler techniques related to software prefetching, including instruction scheduling (Section 2.3.4) and compiler techniques for improving cache utilization (Section 2.3.5).

#### 2.3.1 Hardware prefetching

We use the term "hardware prefetching" to refer to hardware support for bringing items into cache prior to any actual request for the items on the part of the processor. Hardware prefetching schemes are advantageous in that they do not require complicated compiler support, they do not require additional instructions to be added to a program, and they are capable of exploiting information that is available only at run time. Most forms of hardware prefetching rely on the assumption that future memory access patterns can be predicted from past memory access behavior. As a result, they are best suited to applications with fairly simple access patterns that can be easily detected at run-time.

The chief drawback of hardware prefetching is simply that it requires additional hardware, increasing the total system cost and possibly slowing down access to the primary cache. In addition, hardware schemes place more bandwidth demands on the memory subsystem than software schemes, and they tend to fetch more data items that go unused, compared with software schemes. A number of researchers have performed studies to compare the performance of hardware prefetching and software prefetching (see Section 2.3.2); in general, most have concluded that both techniques are roughly equal in terms of overall benefit.

Hardware prefetching has unfortunately not gained widespread acceptance in industry; few contemporary computer designs provide hardware prefetching of the sort described in the works discussed below.

### Prior research on hardware prefetching

Some of the first work on hardware prefetching was by Smith [88, 89]. Smith concentrated on a simple sequential prefetching scheme called *one block lookahead*, in which the hardware fetches block (i+1) on an access to (or cache miss on) block i. He used a cache simulator that analyzed traces generated from a set of programs running on

an IBM mainframe; his results showed that for the machines of the day, hardware prefetching based on one-block lookahead was fairly successful at lowering the miss ratio, provided that the cache line size was small enough.