### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

UMI

## RICE UNIVERSITY

# The Effects of Interconnection Networks on the Performance of Shared-Memory Multiprocessors

by

## Usha Rajagopalan

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

Master of Science

APPROVED, THESIS COMMITTEE:

Dr. J. Robert Jump, Chairman

Professor

Electrical and Computer Engineering

D. John K. Bennett

Associate Professor

Electrical and Computer Engineering

Dr. J. Bartlett Sinclain

Associate Professor

Electrical and Computer Engineering

Houston, Texas

December, 1994

UMI Number: 1377049

UMI Microform 1377049 Copyright 1996, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

IIMI

300 North Zeeb Road Ann Arbor, MI 48103

#### ABSTRACT

# The Effects of Interconnection Networks on the Performance of Shared-Memory Multiprocessors

by

## Usha Rajagopalan

This thesis presents the results of a study of the effect of various interconnection network parameters on the performance of applications running on a scalable shared-memory multiprocessor. We developed a modular simulator for shared-memory multiprocessors called MEMSIM. This simulator, which was developed as a part of the Rice Parallel Processing Testbed, was used in all the experiments described in this thesis. The architecture simulated was a shared-memory multiprocessor with 64 processing nodes, with full bit-map directory-based coherence protocol. The performance of four network topologies: mesh, hypercube, and two shuffle-exchange networks were compared in our experiments. Four applications were used in our experiments: Fast Fourier Transform, Bimerge, Matrix Multiply and Successive Over Relaxation.

The main results of our study can be summarized as follows:

- With constant bisection width, the mesh network outperforms all the other network topologies

- Cache miss rate largely influences the relative performance of different network configurations

# Acknowledgments

I would like to express my gratitude to Dr. Jump for his guidance in defining my goals and keeping me on track to achieve them. I would like to thank Dr. Sinclair and Dr. Bennett for their guidance this past year during Dr. Jump's leave of absence. I would also like to thank all three of them for serving on my thesis committee and for their patient review of my thesis draft.

I would like to thank Sandhya for her help with the cache simulator and all her suggestions that improved this work. I would like to thank Ram and Sridhar for their help and suggestions during our weekly meeting. I would like to thank all my colleagues for making my experience at Rice very memorable.

Last but not the least, I would like to thank my family for their support from near and far in completing this thesis.

# Contents

|   | Abs  | stract                                                           | i   |

|---|------|------------------------------------------------------------------|-----|

|   | Ack  | nowledgments                                                     | iv  |

|   | List | of Illustrations                                                 | vii |

|   | List | of Tables                                                        | x   |

| 1 | Int  | roduction                                                        | 1   |

| 2 | Ov   | rerview                                                          | 3   |

|   | 2.1  | Overview of Interconnection Networks                             | £   |

|   |      | 2.1.1 Overview of Interconnection Network Topologies             | 3   |

|   |      | 2.1.2 Overview of Interconnection Network Switching Mechanisms . | 4   |

|   |      | 2.1.3 Overview of Interconnection Network Routing Algorithms     | 5   |

|   | 2.2  | Motivation                                                       | 5   |

|   | 2.3  | Related Work                                                     | 7   |

| 3 | Sin  | nulation Environment                                             | 10  |

|   | 3.1  | Implementation of MEMSIM                                         | 12  |

|   | 3.2  | Processor Module                                                 | 14  |

|   | 3.3  | Profiling                                                        | 14  |

|   | 3.4  | Cache Module                                                     | 16  |

|   | 3.5  | Write Buffer Module                                              | 17  |

|   | 3.6  | Bus Module                                                       | 18  |

|   | 3.7  | Memory Module                                                    | 19  |

|   | 3.8  | Directory Module                                           | 20        |

|---|------|------------------------------------------------------------|-----------|

|   | 3.9  | Network Interface                                          | 21        |

|   | 3.10 | NETSIM                                                     | 21        |

|   |      |                                                            |           |

| 4 | Exp  | perimental Setup                                           | <b>22</b> |

|   | 4.1  | Processor                                                  | 22        |

|   | 4.2  | Cache                                                      | 24        |

|   | 4.3  | Memory                                                     | 24        |

|   | 4.4  | Directory                                                  | 25        |

|   | 4.5  | Interconnection Networks                                   | 25        |

|   | 4.6  | Coherence Protocol                                         | 28        |

|   |      |                                                            |           |

| 5 | Res  | sults                                                      | <b>32</b> |

|   | 5.1  | Benchmarks                                                 | 32        |

|   |      | 5.1.1 Matrix Multiplication (MMULT)                        | 33        |

|   |      | 5.1.2 Successive Over Relaxation (SOR)                     | 33        |

|   |      | 5.1.3 Fast Fourier Transform (FFT)                         | 34        |

|   |      | 5.1.4 Sorting (Bimerge)                                    | 36        |

|   | 5.2  | Effect of Network Topology                                 | 37        |

|   |      | 5.2.1 Simulation of Networks with Constant Channel Width   | 37        |

|   |      | 5.2.2 Simulation of Networks with Constant Bisection Width | 50        |

|   | 5.3  | Components of Latency of a Cache Line Fetch                | 54        |

|   | 5.4  | Effect of Memory Speeds on Performance                     | 63        |

|   | 5.5  | NETSIM Simulation Complexity                               | 66        |

|   |      |                                                            |           |

| 6 | Cor  | nclusions                                                  | <b>75</b> |

|   | 6.1  | Conclusions on Network Topology Experiments                | 76        |

|   | 6.2  | Conclusions on Comparing Different Link Widths             | 77        |

|              |                                   | vi |

|--------------|-----------------------------------|----|

| 6.3          | Conclusions on Network Complexity | 78 |

| 6.4          | Future Work                       | 79 |

| Bibliography |                                   |    |

# Illustrations

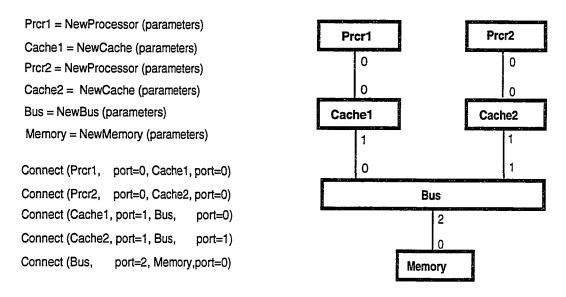

| 3.1  | Routines used to specify architectures in MEMSIM                    | 13 |

|------|---------------------------------------------------------------------|----|

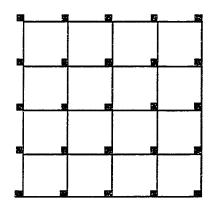

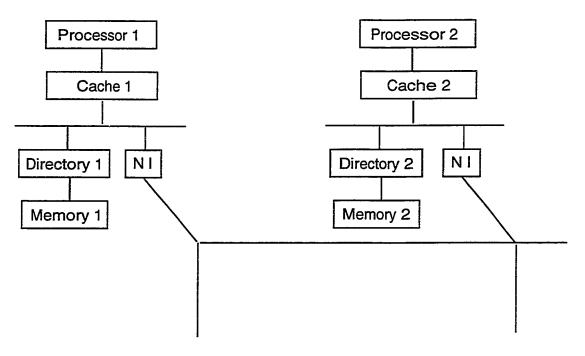

| 4.1  | Scalable Shared-Memory Multiprocessor                               | 23 |

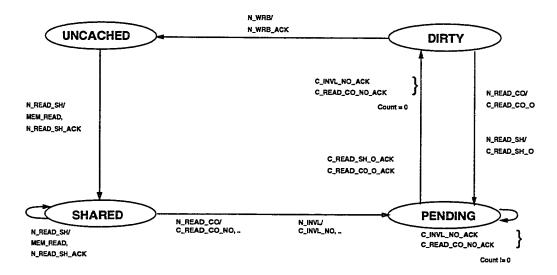

| 4.2  | State Diagram of the Write-Back Coherence Protocol                  | 29 |

| 4.3  | State Diagram Showing Different States of a Directory Line          | 30 |

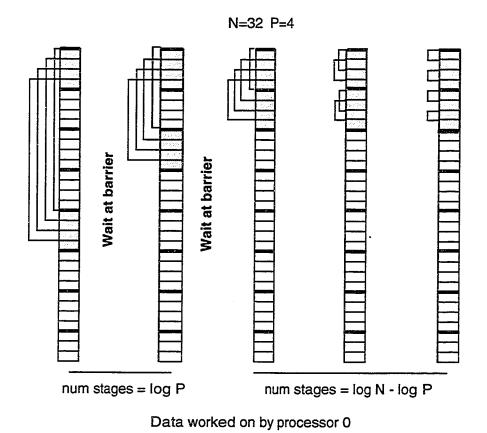

| 5.1  | Communication Pattern of the FFT Algorithm                          | 35 |

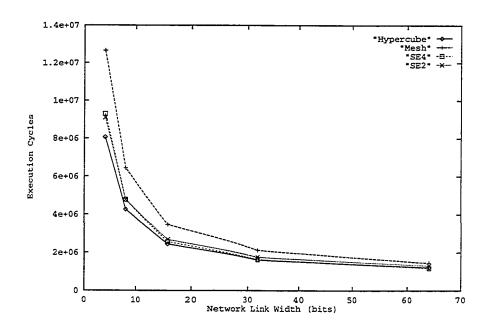

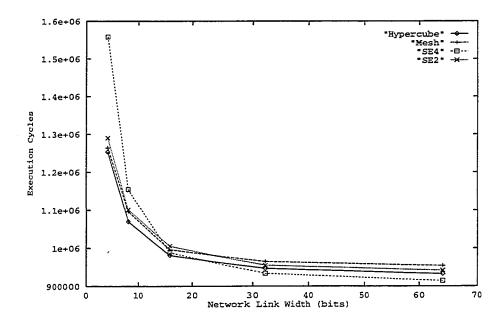

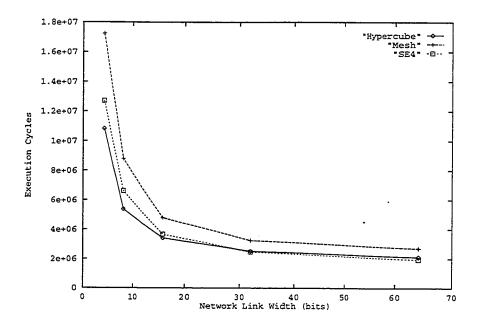

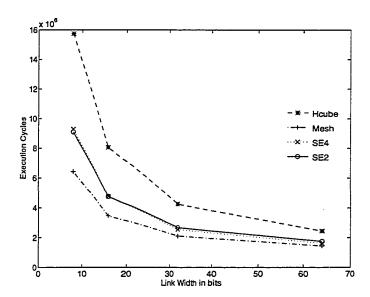

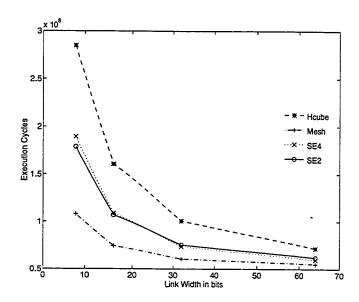

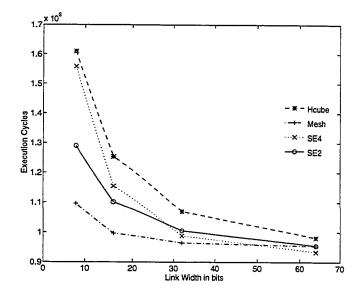

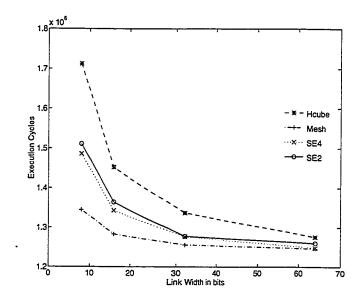

| 5.2  | Performance of Different Network Topologies for FFT                 | 38 |

| 5.3  | Performance of Different Network Topologies for Bimerge             | 39 |

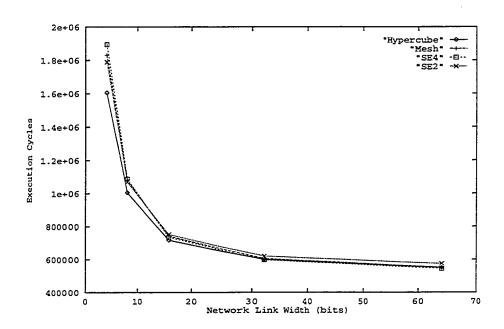

| 5.4  | Performance of Different Network Topologies for SOR                 | 39 |

| 5.5  | Performance of Different Network Topologies for MMULT               | 40 |

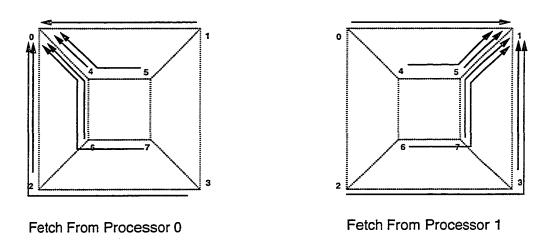

| 5.6  | Communication Pattern of SOR on a Mesh Network                      | 45 |

| 5.7  | Communication Pattern of SOR on a Hypercube Network                 | 45 |

| 5.8  | Communication Pattern of MMULT on a Mesh Network                    | 47 |

| 5.9  | Communication Pattern of MMULT on a Hypercube Network               | 47 |

| 5.10 | Performance of Different Network Topologies for Inefficient MMULT . | 49 |

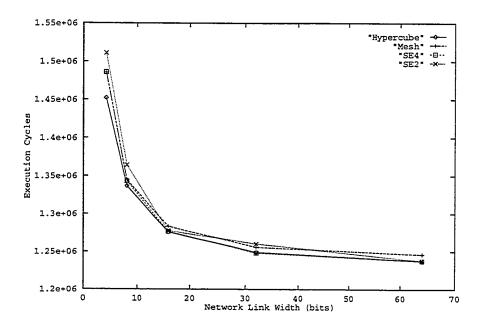

| 5.11 | Performance of Different Network Topologies with Constant Bisection |    |

|      | Width for FFT                                                       | 51 |

| 5.12 | Performance of Different Network Topologies with Constant Bisection |    |

|      | Width for Bimerge                                                   | 52 |

| 5.13         | Performance of Different Network Topologies with Constant Bisection |    |

|--------------|---------------------------------------------------------------------|----|

|              | Width for SOR                                                       | 52 |

| 5.14         | Performance of Different Network Topologies with Constant Bisection |    |

|              | Width for MMULT                                                     | 53 |

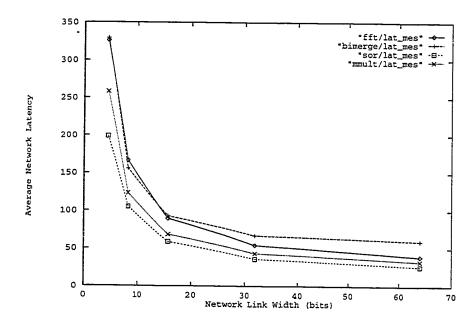

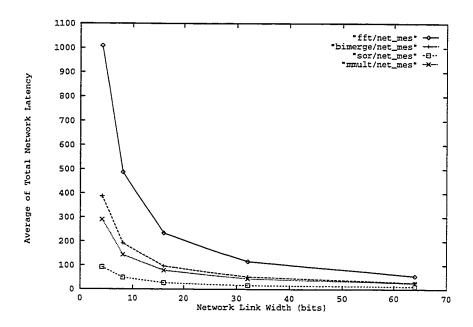

| 5.15         | Sum of Average Network Latency For Request and Reply in a Mesh      |    |

|              | Network                                                             | 56 |

| 5.16         | Sum of Average Network Latency and Port Waiting Time For            |    |

|              | Request and Reply in a Mesh Network                                 | 57 |

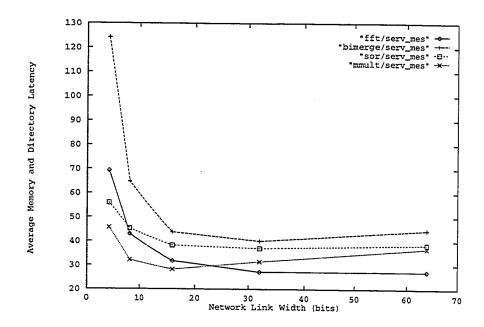

| 5.17         | Average Service Time and Waiting Time at Directory and Memory       |    |

|              | Module in a Mesh Network                                            | 60 |

| 5.18         | Overall Cache Miss Access Latency in a Mesh Network                 | 60 |

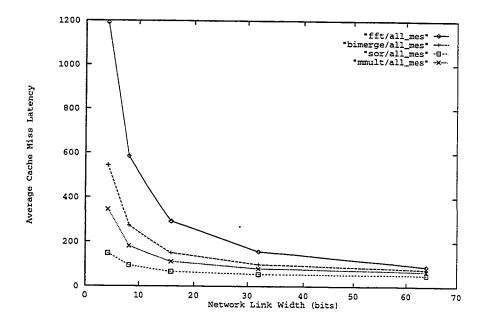

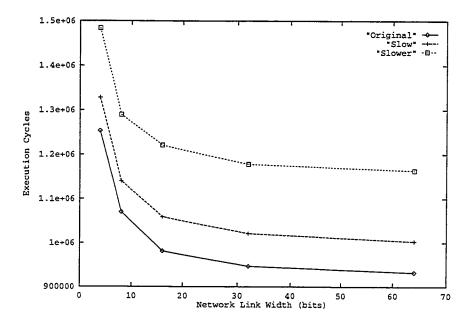

| 5.19         | Performance Difference in FFT as the Memory Speeds are Increased .  | 64 |

| 5.20         | Performance Difference in SOR as the Memory Speeds are Increased .  | 65 |

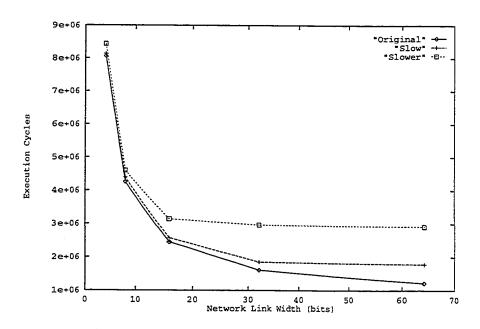

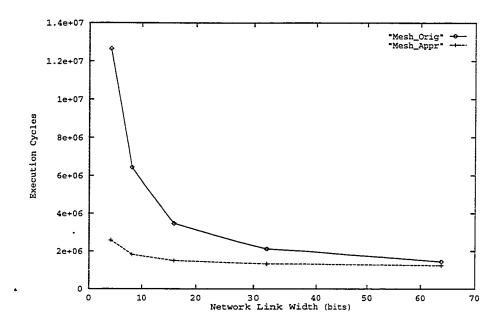

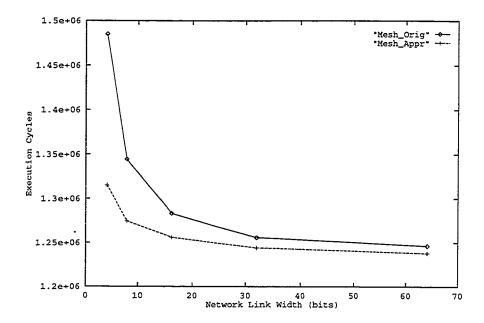

| <b>5.2</b> 1 | Execution Time Predicted by Detailed Network Simulation and         |    |

|              | Approximate Network Simulation for FFT                              | 67 |

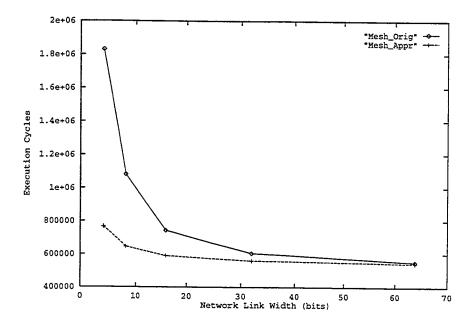

| 5.22         | Execution Time Predicted by Detailed Network Simulation and         |    |

|              | Approximate Network Simulation for Bimerge                          | 68 |

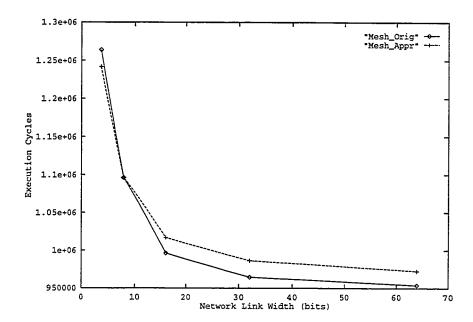

| 5.23         | Execution Time Predicted by Detailed Network Simulation and         |    |

|              | Approximate Network Simulation for SOR                              | 69 |

| 5.24         | Execution Time Predicted by Detailed Network Simulation and         |    |

|              | Approximate Network Simulation for MMULT                            | 70 |

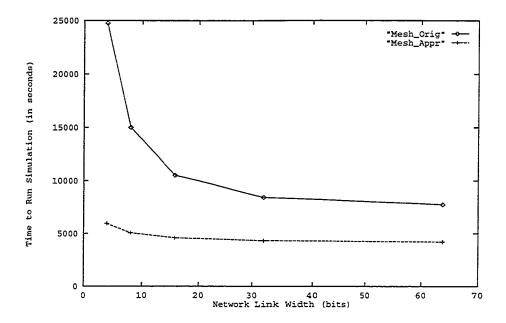

| 5.25         | Simulation Time Taken by Detailed Network Simulation and            |    |

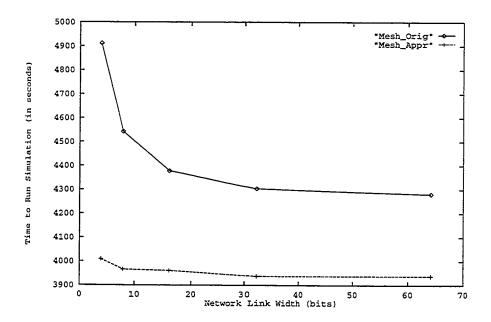

|              | Approximate Network Simulation for FFT                              | 71 |

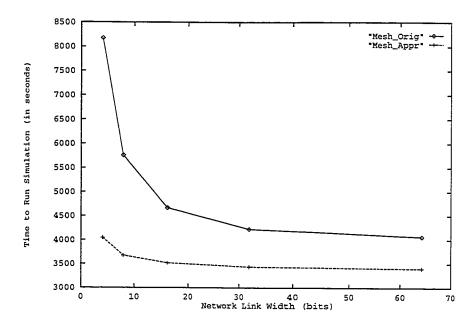

| 5.26         | Simulation Time Taken by Detailed Network Simulation and            |    |

|              | Approximate Network Simulation for Bimerge                          | 72 |

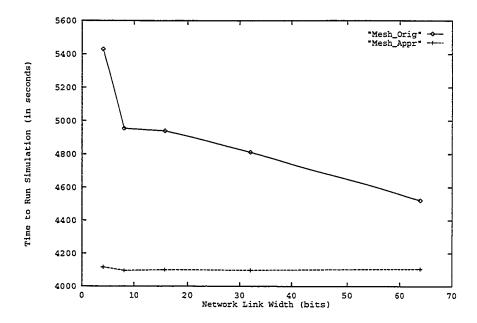

| 5.27         | Simulation Time Taken by Detailed Network Simulation and            |    |

|              | Approximate Network Simulation for SOR                              | 73 |

| 5.28 | Simulation Time Taken by Detailed Network Simulation and |    |

|------|----------------------------------------------------------|----|

|      | Approximate Network Simulation for MMULT                 | 74 |

# Tables

| 5.1 | Applications Used in Study                                      | 36 |

|-----|-----------------------------------------------------------------|----|

| 5.2 | Comparing the Performance of Shared-Memory Multiprocessors with |    |

|     | Different Network Topologies                                    | 38 |

| 5.3 | Equivalent Link Widths                                          | 51 |

| 5.4 | Latency of the Two Packet Sizes at Various Link Widths          | 56 |

| 5.5 | Percentage Improvement in Cache Miss Latency with a Mesh        |    |

|     | Network When Link Width is Increased                            | 61 |

| 5.6 | Percentage Improvement in Performance with a Mesh Network When  |    |

|     | Link Width is Increased                                         | 61 |

| 5.7 | Percentage Improvement in Performance as the Link Widths Are    |    |

|     | Increased. (2 Memory Speeds)                                    | 66 |

# Chapter 1

## Introduction

This thesis studies the effect of various interconnection networks and interconnection network parameters on the performance of applications running on a scalable shared-memory multiprocessor. We developed a modular simulator for shared-memory multiprocessors called MEMSIM. This simulator, which was developed as part of the Rice Parallel Processing Testbed (RPPT), was used in all the experiments described in this thesis.

It is becoming increasingly more difficult to satisfy the demand for high performance computer systems by using uniprocessors. As a result, most new high performance computing systems are multiprocessors constructed from commercial microprocessors. Two programming models have been developed for these systems, the distributed-memory programming model and the shared-memory programming model.

Programming for a distributed-memory programming model is felt to be harder than for a shared-memory model, since the programmer has to provide explicit statements to facilitate data communication between processors. Examples of multiprocessors which support the distributed-memory programming model include the Intel Paragon [9], the Thinking Machine Corporation's CM-5 [12], and the Cray T-3D [31]. Shared-memory multiprocessors have received a lot of attention because the shared-memory programming model is felt to be easier to use. A majority of available shared-memory multiprocessors use a single-bus and are not scalable. Examples of such systems include the Sequent Symmetry [33] and the Encore Multimax [10]. The

bus, which is a central resource, becomes a bottleneck when too many high performance processors use the bus to access memory. A single-bus shared-memory system can only support about 30 processors.

Multiprocessors can be scaled to more than a few tens of processors, by using an interconnection network that can connect a few hundred or even a few thousand processors without becoming a bottleneck. Such large-scale multiprocessors can support the shared-memory programming model by using a directory-based coherence protocol [6]. A simple directory-based coherence protocol has a directory entry associated with each cache line-sized block in memory. This directory keeps track of nodes that have cached a copy of that line and the current state of the line. This information can be used to send messages to the caches involved in a specific transaction instead of broadcasting information about each transaction to all caches. The Stanford DASH multiprocessor [32] and MIT's Alewife [3] use the directory-based coherence protocol. This thesis studies the performance of interconnection networks in a large-scale shared-memory multiprocessor using a directory-based coherence protocol. This study is conducted by simulating the execution of parallel applications on such a multiprocessor.

The performance of four network topologies: mesh, hypercube, and two shuffle-exchange networks is compared. The various components of the network latency is analyzed and the factors in the application that affect these components is studied. The tradeoff between time to run a detailed network simulation and the accuracy of the results predicted by the simulation is also studied.

Chapter 2 gives some background information, an overview of the project, and related work. Chapter 3 describes the MEMSIM simulator. Chapter 4 describes the simulated architecture and the parameters used in the experiments. Chapter 5 presents and discusses our results. Chapter 6 provides conclusions and future direction of this research.

## Chapter 2

## Overview

This chapter provides an overview of interconnection networks, describing the different topologies, switching methods and the routing algorithms used in networks. It also describes the network types that are studied in this thesis, a motivation for studying these particular networks and the motivation for studying the effect of networks on the performance of shared-memory multiprocessors. This chapter also describes related work done in the study of interconnection networks.

#### 2.1 Overview of Interconnection Networks

The interconnection network is a very important component in a multiprocessor. The purpose of an interconnection network is to provide communication paths between the modules of a parallel system. The different parameters to be considered during the design of an interconnection network are the network topology, the routing algorithm, switching mechanism and the bandwidth of the network.

#### 2.1.1 Overview of Interconnection Network Topologies

The simplest network topology is a bus, a single path that all the modules must share. This is not scalable in terms of performance, since only one module can send data at a time. The crossbar network represents the other extreme where each module has a direct connection to every other module in the system. This is not scalable in terms of cost since it requires  $N^2$  switches to connect N modules. In between these two extremes there are a variety of network topologies that one can choose from. They

are generally classified as direct networks or indirect networks. In direct networks every switch in the network is also connected to a processing node. The direct k-ary n-cube networks have n dimensions with k nodes in each dimension. The 2-D torus and the hypercube, which is a binary n-cube, represent two extremes of this class of networks. Indirect networks, also known as multistage interconnection networks, have the characteristic that all modules connected to the networks are equidistant from each other. The bisection width of a topology is the minimum number of channels that must be cut to divide the network into two equal halves. It is used as a measure of network cost, since the complexity of a connection is wire-limited. The different network topologies studied in this thesis are mesh, hypercube and the shuffle-exchange network.

### 2.1.2 Overview of Interconnection Network Switching Mechanisms

Switching methods include packet-switching, circuit-switching, virtual cut-through [30] and wormhole routing [14]. In packet-switching, also known as store-and-forward, the entire packet is stored in the buffer of an intermediate node before it is forwarded to the next node determined by the routing algorithm. In this case the latency of a packet to traverse the network is proportional to the product of the size of the packet and the distance (number of hops) traversed by the packet. In circuit-switching a path is first established between the source and destination nodes and this path is reserved for the packet. The tail of the packet tears down the path. This can achieve better performance than packet-switching for long packets. Virtual cut-through sends a packet through the network without first establishing a circuit. As long as there is no blocking the head of the packet makes progress through the network. The other flits (smallest unit of data that can be transferred between two switches) of the packet can be spread out along the path, depending on the length of the packet. When the packet is blocked at a node, trailing flits catch up and are buffered at that node.

The difference between this and wormhole switching is that in the latter, the switch buffers do not have to be large enough to hold a whole packet. The flits of a blocked packet are distributed along the network in different buffers. The routing algorithms are more limited for wormhole routing, due to the possibility of deadlock. Wormhole routing is being used widely in current generation multiprocessors. This thesis studies the performance of wormhole-routed networks.

### 2.1.3 Overview of Interconnection Network Routing Algorithms

Routing determines the path selected by a packet in order to reach its destination. Routing can be classified as deterministic or adaptive. In deterministic routing, also known as oblivious routing, the path is completely determined by the source and destination pair. Adaptive routing takes the state of the network into consideration and can alter the path of a packet to avoid congestion in the network. The routing algorithm is minimal if the path selected is a shortest path between the given source and destination pair. One deterministic routing scheme that is guaranteed deadlock-free for wormhole routing is a dimension-ordered routing scheme called e-cube routing [35]. Adaptive routing algorithms for wormhole-routed networks, which are deadlock-free, are complicated and can be expensive and slow to implement [35]. In this thesis, the study of networks is restricted to deterministic routing.

#### 2.2 Motivation

Shared-memory multiprocessors that scale up to a few thousand processors seem viable. Much research is focused on making such systems efficient. In particular, efforts are made to hide or tolerate the high memory access latencies involved in such systems. One technique is to provide fast context switching in hardware. Several threads can be kept active on each processor at the same time and a processor can switch among these threads to hide individual access latency [44]. Dynamic instruction scheduling

at the processor can increase processor utilization, by allowing instructions to execute out of sequence whenever earlier instructions are waiting on a data access, provided there is no data dependency [21]. Such techniques attempt to increase processor and network utilization. Previous simulation experiments used to evaluate these techniques typically have ignored contention in the network. While this could give an estimate of the best performance gain possible, if the network performance does not match the performance of the rest of the system, these gains will be unattainable.

Interconnection networks are important components of multiprocessors. The rate of execution by a single processor is increasing, through increased clock speed, instruction pipelining and the use of multiple functional units with super-scalar execution. Without the proper design of interconnection networks the communications among parallel threads may result in significant performance degradation due to network latencies and throughput limitations.

Interconnection networks have been studied for a long time. Much attention has been given to the design and performance analysis of interconnection networks. Numerous network topologies have been proposed and evaluated. A survey can be found in [18]. The performance analysis of networks has mostly been done using mathematical models and stand-alone simulations ([16, 1, 2, 13]). However, such performance evaluation techniques do not always capture the access patterns of real programs. One of the motivating factors in this work is to study the performance of networks driven by the execution of an application on a shared-memory multiprocessor.

This thesis compares the performance of four different network topologies, the mesh, the hypercube and two shuffle-exchange network configurations. These topologies were chosen because commercial multiprocessors have been built using mesh, hypercube and multistage interconnection networks. The hypercube has been used in several multiprocessors, starting with a research machine from Caltech called the

Cosmic Cube [40]. Other multiprocessors with hypercubes include the iPSC and iPSC/2 [8] from Intel, NCUBE/ten [11], and CM-2 [25], an SIMD machine from Thinking Machines Corporation. More recently Intel has abandoned the hypercube architecture and is using a mesh network in the Paragon [9]. The Cedar parallel processor from the University of Illinois [19] uses a shuffle-exchange network with an 8x8 crossbar at each switching node.

The performance of the different network topologies are compared when they have an equal link width and when they have a constant bisection width. Also, the performance of each network topology is studied for different link widths and in order to find an optimal bandwidth for a particular network topology. For all of these experiments the other parameters of the system, such as speed of the processor and memory sub-system and size of the caches, are fixed and the network performance is studied under these fixed parameters. All the system parameters reflect current technology and the technology trends expected. The network performance is also studied at different ratios of processor speeds to memory speeds, since we do not expect DRAM performance to keep up with the improvements in processor performance. All our experiments use wormhole-routed networks since this is the routing scheme of choice in most commercial multiprocessors.

### 2.3 Related Work

Interconnection networks have been studied for a long time. The performance analysis of networks has mostly been done using mathematical models and stand-alone simulations ([16, 1, 2, 13]). [29] presents an algebraic theory based on tensor products for modeling direct interconnection networks. Ponnuswamy et al. evaluate the performance of the network in the CM-5 multiprocessor experimentally [37]. Chittor and Enbody evaluate the performance of wormhole routed meshes with the use of the Symult 2010 multiprocessor [7]. They use experimental results to show that the path

length of the message does not adversely affect performance, but that contention for network resources does. Neither of these studies use complete applications, but drive the network with messages of varying sizes and different network traffic patterns.

There has been a lot of work to improve a particular algorithm for a specific network topology. Examples include the implementation of FFT on hypercubes [45] and an implementation of FFT on the butterfly network [34]. Such work studies the network performance with respect to a specific algorithm and may not be useful in the design of a general-purpose multiprocessor. [4] presents the results of running the NAS benchmarks on several parallel processors and supercomputers, including the iPSC/860, which has a mesh network and the BBN TC2000, which has a butterfly interconnection network. However, no attempt is made to analyze the results and determine whether the differences are due to the network or due to other differences in the two systems. In fact, it is very difficult to separate the performance effect of networks from other factors and might require some diagnostic hardware to be installed in the machines.

Abraham and Padmanabhan compared the performance of the direct binary n-cube with the indirect binary n-cube network [1]. The performance evaluations are done for equiprobable distribution of message destinations. They also evaluated the network under special conditions such as broadcasts and hot-spots. The performance analysis was done for packet-switched networks. They found that the direct network performs better. Dally compared the performance of networks belonging to the class of direct k-ary n-cube [13]. He compared the networks for wormhole routing under a constant bisection width constraint for a network size of 256, 16 K, and 1 M nodes. He arrived at values for the actual latency and latency with contention when the traffic in the network is a certain fraction of the total network bandwidth. His results show that the 2D-torus network performs best. Agarwal expanded on this work in [2], by calculating the latency of k-ary n-cube networks when the switch latency is

greater than the link latency. He found that when the switch delay is higher, 3D and 4D tori perform better than the 2D-torus.

The simulator used in the experiments described in this thesis is an executiondriven simulation testbed called the Rice Parallel Processing Testbed (RPPT). As a part of this thesis we extended RPPT to support shared-memory simulation, by developing a cache-memory hierarchy simulator called MEMSIM. A detailed network simulator called NETSIM [27] is a part of RPPT and is used in our experiments. Tango [15], Proteus [5] and an earlier RPPT shared memory simulator [17] are other execution-driven simulators running on uniprocessors. The Wisconsin Wind Tunnel (WWT) [39] executes on a CM-5 using a form of distributed discrete-event simulation. A major difference between MEMSIM and the above mentioned simulators is that MEMSIM interfaces to a detailed and versatile interconnection network simulator (NETSIM). NETSIM can simulate different types of routing such as virtual cutthrough, worm-hole routing and store-and-forward. Most interconnection networks can be built from the modules provided by NETSIM. The WWT and DASH [32] simulator (using Tango) approximate the effect of the network with constant latency to reach any destination. Proteus allows the user to simulate interconnection networks with store-and-forward routing or approximate the effects of the interconnection network using an analytical model. Store-and-forward routing is not used in newer parallel machines since cut-through routing techniques have lower latency. The WWT simulates one target processor per host processor of the CM-5, limiting the number of simulated processors to the size of the CM-5.

# Chapter 3

## Simulation Environment

The simulator used in the experiments described in this thesis is an execution-driven simulation testbed called the Rice Parallel Processing Testbed (RPPT). As a part of this thesis we extended RPPT to support shared-memory simulation, by developing a cache-memory hierarchy simulator called MEMSIM. A detailed network simulator called NETSIM [27] is a part of RPPT and is used in our experiments to model the interconnection networks. This chapter provides an overview of MEMSIM.

In the design of parallel machines, simulators provide an effective tool to evaluate different architectural features. Simulations driven by the execution of applications have proven to be fairly accurate and are cost-effective when compared to building hardware prototypes. Simulators that are not driven by real programs, but instead use analytical models or are distribution-driven, are not sufficiently accurate for many purposes, because they do not accurately model the behavior of real programs in this way. Different techniques used in the simulation of the execution of an application on a target architecture are instruction-level emulation, trace-driven simulation and execution-driven simulation.

Trace-driven simulations use address traces collected from a run of the program on a hardware machine. Traces are collected from a machine when an application is running in that machine. The traces are then input to a simulator modeling the target architecture. This simulation technique has been used for a long time. One of the advantages of trace-driven simulation is that one does not need to have access to the source code of the application. However, trace-driven simulation is not very accurate

in the case of multiprocessors because it is difficult to obtain accurate interleaving of address traces from different processors in the multiprocessor. Any interleaving inherent in the trace may not be valid for the execution on the target architecture. Another disadvantage of this technique is that the address traces generated for an application will generally require large amount of storage space. Instruction-level simulators emulate each instruction of the target machine in software. Such simulations can be quite expensive in terms of the time taken to simulate the target architecture.

In the execution-driven simulation approach, the machine language instructions of the application program are executed directly on the simulation host. The program is modified using a profiler that inserts instructions in every basic block of the program to increment the simulation time as the program executes. In systems with caches, the simulator has to determine whether each access is a hit or a miss in the cache, and in the case of a miss, simulate a new cache line fetch. The global clock of the simulation is updated during cache accesses and other potential processor interaction points. When the memory address can be determined statically, the profiler generates these addresses and writes them to a trace file. The profiler inserts code into the user program to generate all other addresses dynamically.

The overhead of emulating each instruction is avoided in execution-driven simulation, making it faster than instruction-level simulators. Since the execution-driven simulation executes all instructions on the host machine, the cache data structure in the simulator does not maintain a copy of the cache line. The simulator only maintains the tags and state of the simulated cache. This makes this type of simulator more space efficient than instruction-level simulators.

MEMSIM is a modular execution-driven simulator for shared memory architectures. It is implemented as an extension to a discrete-event simulator called YACSIM [26], which was developed as part of the Rice Parallel Processing Testbed (RPPT). MEMSIM can also be driven by traces. MEMSIM was used to obtain all results pre-

sented in this thesis. MEMSIM interfaces with NETSIM [27], a general-purpose interconnection network simulator that is also implemented as an extension to YACSIM. The different modules provided by MEMSIM are cache, write buffer, bus, directory, memory, network interface and processor. The features of these modules are explained in the following sections. The user specifies a target architecture in MEMSIM by initializing the necessary modules and then connecting them to configure the architecture. These modules may be chosen from the set of modules already implemented, or may be supplied by the user.

### 3.1 Implementation of MEMSIM

All modules in MEMSIM are implemented using YACSIM activities. YACSIM implements two types of activities, events and processes. Activities can be scheduled to "happen" in the future. Each YACSIM activity when created is assigned a C-procedure that specifies its action. This procedure is called the body of the activity. A YACSIM process can temporarily suspend execution and continue execution at the next line of the process body when it is reactivated. This is achieved by saving the current context when the process is suspended and restoring the context when it is rescheduled. A YACSIM event starts executing in the beginning of the event body each time it suspends and is reactivated. If MEMSIM modules are implemented as processes, the overhead associated with suspending and reactivating the process can get quite expensive when several MEMSIM modules have to be scheduled to complete one remote memory access. The modules in MEMSIM are implemented using YACSIM events. By changing the structure of the event body to keep track of the last line executed before suspension, events can be as flexible to use as processes.

During the design and development of MEMSIM much emphasis was given to modularity. While developing such a simulator, the developer cannot foresee all the different architectures that are going to be evaluated using the simulator. Therefore it is important that the tools are provided for the user to customize a module or implement a new module altogether and have it work with existing modules.

Each module in MEMSIM has a data structure that is a derivative of a base module type. The user sets up the architecture to be simulated, by creating the necessary number of modules and then connecting the modules together using MEMSIM calls (see Fig. 3.1). When a module is created a YACSIM event is initialized and associated with that module. The body of the event is the main function that acts on the data structure of that module in order to update it. Scheduling the event associated with a module does not have any undefined side-effects on other modules. This makes it possible for the user to connect modules as necessary or to define and use new modules connected to existing MEMSIM modules.

A request packet is created and initialized at the processor module, which is the first module entered during simulation. From there the request is sent from one module to another until it is satisfied. For example, a request would be satisfied in

Figure 3.1: Routines used to specify architectures in MEMSIM

the cache if there is a cache hit. Otherwise, the request would have to be sent to the next level in the memory hierarchy. When a request is satisfied, it travels back to the processor and control is returned to the user program. If a module is connected to several modules, a routing function is used to determine the next module requested.

The different modules supported by MEMSIM include Processor, Cache, Write Buffer, Bus, Directory, NETSIM interface and Memory. A short description of the features of each module follows.

#### 3.2 Processor Module

In execution-driven simulation the application program is executed directly on the machine on which the simulation runs. The application program is initially augmented with lines of code by a program called the profiler. The code added to the application program by the profiler helps the simulation to keep track of the number of cycles executed and provides hooks to simulation modules such as caches. Currently RPPT supports a profiler for the SPARC architecture when used as a shared-memory multiprocessor simulator. Therefore the processor module in MEMSIM simulates the SPARC architecture. The next section provides an overview of the MEMSIM profiler.

## 3.3 Profiling

The profiler works on the assembly code of the application program. In order to account for the time taken to execute the program the profiler inserts a few instructions at the end of each basic block to increment the timing variable of YACSIM by the number of cycles it takes to execute that basic block. Two versions of the profiler are available for use with MEMSIM. The user can choose to simulate both instruction and data accesses to the cache, or simulate the data accesses alone (assuming in this case that all instruction accesses hit in the cache).

In order to simulate the data accesses to the cache the profiler inserts code before each instruction that has a data access (various load and store instructions in the case of the SPARC), to do the following:

- save global registers

- extract the address for the data access and write the address to a variable

- determine the type of access

- call the cache module with this information

- restore global registers after the return from the cache module

The profiler saves the global registers into the data structure for the current process.

When instruction accesses are also simulated, the profiler determines the instruction addresses at profile time. The user provides the profiler with assembly code of the application program as well as an executable of the program. This executable is compiled by the user from the application program before the profiler augments the code. This gives the profiler an access to the accurate address trace of the program. However, this executable is only used by the profiler and the profiled application program is the one that is actually executed.

The profiler extracts the instruction addresses from the symbol table of this executable and writes the static address trace into a file. Labels are inserted into the static trace to indicate basic block boundaries. It must be mentioned here that static address traces are usually much shorter than dynamic address traces that are generated in a trace-driven simulation environment. This is because programs usually spend about ninety percent of their time looping in ten percent of the code. The instruction accesses are simulated at the beginning of each basic block for all instruction addresses in that basic block. The profiler inserts code similar to that mentioned above for the data accesses, at the beginning of each basic block. During each call,

MEMSIM simulates all instruction accesses for the basic block (by reading the address trace produced by the profiler) before returning to the user program.

#### 3.4 Cache Module

The cache module simulates a processor cache. It can be a unified cache, a data cache, or an instruction cache. It can also be used at any level in a hierarchy of caches. The cache module is implemented as a data structure that stores the tag and state for each cache line. The user can set the size of the cache, the line size, the set associativity, the replacement policy, and the coherence protocol when the module is initialized. It supports any cache size starting from 1 KB, limited only by the amount of memory available for the simulation. The module can also be used to model an infinite cache. Set size may be any power of two, making MEMSIM capable of simulating a direct-mapped cache, a fully associative cache or any set size in between. The replacement policies supported by the cache module are Least Recently Used (LRU) and First In First Out (FIFO). The cache module can be customized to support any coherence protocol desired. When the cache module is initialized, the coherence protocol is supplied to it as a pointer to a function. The user can simulate one of the coherence protocols supported by MEMSIM or provide a function to simulate any other coherence protocol.

The coherence protocols supported by MEMSIM include Write-Through with Update, Write-Through with Invalidate, Write-Back with Invalidate and Write-Through when Shared. The Write-Through caches update the main memory each time there is a write to the cache. The Write-Through with Update protocol updates other caches that have a copy of the data when one node writes through to memory. The Write-Through with Invalidate protocol invalidates other cached copies when one node writes through to memory to memory. In Write Back caches, on a write access to a shared line, the cache sends a request to invalidate all other cached copies and

obtain an exclusive copy. Subsequent writes to the line are completed at the cache. This cache has the only valid data in the system, and the line is in the dirty state. When the cache wants to replace the line or another processor wants to read or write this line, the data is written back to main memory. With the Write-Through when Shared protocol, if the line is in shared state, on a write access the data is written through to memory. At this time all other copies are updated. When this cache has the only copy of the line, writes are completed locally. In this case also, the line is dirty and transferred to memory later.

Caching is said to be adaptive, if the programmer has control over the coherence protocol. MEMSIM supports adaptive caching by allowing the user to inform the simulator that certain address ranges are associated with a particular coherence protocol. The cache type must also be initialized to be adaptive and given a default coherence protocol. The cache module checks for the coherence type of each access when it is referenced for the first time. If there is no entry for that particular address, the default coherence protocol is used. The user can also specify that certain data items are non-cacheable.

#### 3.5 Write Buffer Module

A write buffer is used to buffer a write accesses, so that the processor requesting a write can proceed without waiting for the write to complete. Buffering can improve performance of the system when there is significant delay between processors and memory modules, due to network latency and/or contention. The write buffer sends the write transaction to the appropriate next module when the interconnection is free. It also keeps track of forwarded write transactions until an acknowledgment comes back. The write buffer has to be concerned with the ordering among reads and writes and when the accesses can be issued. The implementation of the write buffer largely determines the consistency model of the system. A brief description of

different consistency models are given in [20]. The weaker consistency models take advantage of the synchronization statements inserted by the programmer and attempt to keep the system consistent only at the synchronization points. The implementation of different consistency models in MEMSIM are confined to the write buffer module.

When MEMSIM is used without write buffer modules, the system is sequentially consistent. The write buffer module implements two types of consistency models, processor consistency and release consistency. When initializing the write buffer module, the user can choose the size of the buffer and the consistency model, and supply the module with a pointer to the function implementing the coherence protocol. The write buffer must refer to a coherence function since there can be a coherence request for a cache line that is waiting at the write buffer and the transaction type for this line could change as a result of that coherence request.

#### 3.6 Bus Module

The bus module simulates the bus connecting multiple processor nodes. The bus module simulates the time to complete a transaction and the time spent waiting for the bus. It can also simulate a snooping coherence protocol when the user initializes this module with a pointer to a coherence function.

MEMSIM implements two type of bus modules, one that supports split transaction and one that does not. A non-split transaction bus sends a request to the next module (usually the memory) and the bus is held until the reply is sent back. A split transaction bus sends a request to the next module and does not wait for the reply. The bus may transfer another request while the memory module completes the access. The memory module will then have to arbitrate for the bus to send the reply back.

If the bus module is initialized with a pointer to a coherence function, the bus module has to also complete the coherence actions of each transaction (such as invalidating or updating other caches). It is more inefficient to simulate snooping as it occurs in a real system since this involves each cache module having knowledge of every transaction on the bus. Instead, for each transaction the bus module updates a data structure that keeps track of all the caches that have a copy of each line. When the cache replaces a line, it calls a sub-routine to update the bus data structures. Therefore the bus module always has the current list of caches that have a copy of a line.

On each transaction the bus module calls the coherence routine of the bus with the transaction type. The coherence routine returns a list of caches (if any) that must receive a coherence message in order to complete the current transaction. For instance when implementing the Write-Back with Invalidate coherence protocol, a write request to a shared line will have to invalidate all copies of the line. When such a write transaction is sent on bus, the bus module sends an invalidation message to the caches on the list returned by the coherence routine. The write transaction completes only after all the necessary caches have been invalidates. This achieves the same result as a snooping coherence protocol.

## 3.7 Memory Module

The memory modules in MEMSIM simulate the time to access the module. The user can specify the time to complete a read or a write access to a word in the burst mode and in the individual access mode when the module is initialized. When the memory module is accessed, the data is always assumed to be present. That is, page faults are not simulated. If the user wanted to simulate virtual memory, some of the cache data structures, could be used to maintain page tables. Also the cache routines used to determine a hit or a miss in the cache can be adapted to determine the hit or miss of a page in memory.

## 3.8 Directory Module

The directory module is used in systems that implement directory-based coherence protocols. This module is used in systems where processors communicate with one another through an interconnection network that does not support an efficient broadcast mechanism. It may also be impossible to achieve atomic broadcasts in such systems. Therefore a directory entry is maintained for each cache line-sized block in memory. This entry maintains the state of the line and either a list of caches that have a copy of the line or a pointer to such information. A more detailed description of various directory schemes can be found in [6]

MEMSIM implements a full-map directory scheme. Each directory entry consists of a bit vector and some state bits. The size of the vector is equal to the number of processors in the system. Each bit in the vector is set or cleared depending on whether or not that particular processor cache has a copy of the line. Currently Write-Back with Invalidate coherence protocol is supported in this module. Other protocols can be supplied by the user as a pointer to a function when the module is initialized.

MEMSIM allows the user to map program data to a specific memory module. The user can also classify data as private, in which case it is assumed to be mapped to the local memory of that node. The user can map the program data by making calls in the user program to associate a certain address range with a particular memory module. From this information, the cache module determines the home node of a given request, when it misses in the cache. The request is routed to the appropriate directory module, and the directory module follows the coherence protocol to keep the data coherent.

#### 3.9 Network Interface

NETSIM is a general-purpose interconnection network simulator. The Network Interface module is the interface between MEMSIM and NETSIM. This module essentially simulates the network ports. It converts MEMSIM packets into NETSIM packets and vice versa. When this module is created, the user must provide the buffer size of the network ports. There are two type of network interface modules in MEMSIM. One of them can be used to send packets into the network and the other can be used to receive packets from the network.

This module is specially designed to work with directory-based architectures that require two networks in order to avoid deadlocks. The necessity for two networks is described in the Section 4.5. One of the two networks is used to send memory or coherence requests to a remote node or to receive requests from a remote node to the memory or cache module in this node. The other network is used to send (receive) replies. Therefore each network interface module also requires pointers to two NETSIM ports when initialized.

#### 3.10 NETSIM

NETSIM is a general-purpose interconnection simulator. It can be used to construct and simulate a wide range of network models, including both direct and indirect networks. It is designed to simulate large networks that use modern routing techniques, such as worm-hole and virtual-cut-through routing, but can also simulate networks that use store-and-forward routing. All the experiments described in this thesis were done for networks using worm-hole routing. The NETSIM Reference Manual [27] and a related paper [28] provide more details about this simulator.

# Chapter 4

# Experimental Setup

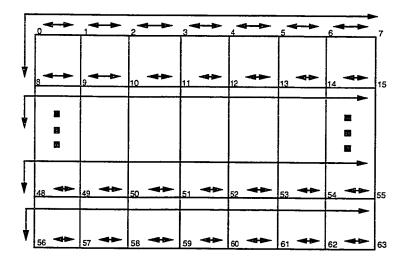

This chapter describes the architecture simulated. The architecture of the shared-memory multiprocessor studied is shown in Figure 4.1. The figure shows the mesh network, although we simulate different network topologies. A 64-node system is simulated, with each processing node consisting of a processor, a cache, a memory, a directory module, and a network interface. Each of these modules and the parameters pertaining to each module are described in the following sections.

#### 4.1 Processor

As described in Section 3.3, the processor is not simulated in detail in an execution-driven simulation. The profiler for the SPARC architecture (which is not super-scalar) is used with all simulations presented in this thesis. The simulator keeps track of simulated time in terms of the number of processor cycles executed instead of in seconds. Therefore the processor cycle time is not directly relevant. However in order to determine the access time of other modules in the system in terms of processor cycles, it is necessary to determine the processor speed. We assume a processor speed of 50 MHz.

Figure 4.1: Scalable Shared-Memory Multiprocessor

#### 4.2 Cache

Each processing node has one cache module. The caches are 32 KB in size, 2-way set associative and have a cache line size of 32 bytes. A survey of current workstations shows that cache sizes vary between 16 KB and 4MB, with 256 KB being the most common configuration. We chose to simulate a smaller cache, in order to scale down the problem sizes and be able to run experiments in a reasonable amount of time. Although larger set sizes in the cache can lead to better performance, it has been shown that the maximum performance gain is obtained when going from a direct-mapped cache to a set size of two [41]. Therefore we simulate a 2-way set associative cache. Only data accesses to the cache are simulated. We assume that all instruction accesses hit in the cache. This is a reasonable assumption, since experiments have shown that even small instruction caches have very high hit rates [42].

# 4.3 Memory

Each processing module has one memory module. When the memory module is accessed for a given address, the page is always assumed to be present. That is, virtual memory is not simulated. We simulate a memory module with a 60ns access cycle and a fast page mode access time of 40ns. This is equivalent to 3 processor cycles for the initial access and 2 cycles for each additional word accessed. The data paths inside each node are 64 bits wide. Therefore the memory module takes 9 cycles to return a 32-byte cache line on a read. For simplicity we assume that the writes take just as long. Wherever possible, the program data of applications is mapped to the memory module close to the processor that uses the data. In Section 5.1, when the applications used in this thesis are described, the data mapping used for that application is also described.

## 4.4 Directory

The directory module is used to maintain coherence in the system. A directory module is associated with the memory module in every node. Each cache line in memory has a directory entry associated with it. A full bit vector directory scheme is simulated in all our experiments. In this scheme, each directory entry consists of a vector and some state bits indicating the state of the line. The size of the vector is equal to the number of processors in the system. Each bit in the vector is set if the corresponding processor cache has a copy of the line. This type of directory scheme is not as scalable as chained directories, or a limited directory with software extensions. However, this scheme is the most efficient in terms of the number of messages sent and the overall access time. It has been shown that this scheme can be made more scalable by using a cache of directory entries instead of having a directory entry for every line in the physical memory [23].

Since the directory module is associated with the memory module, it will most probably be implemented in DRAM technology. Most accesses to the directory data structure are Read-Modify-Write (RMW). This can take as much as 115 ns in a DRAM with a 60 ns access time. This translates to approximately 6 processor clock cycles for each access. The directory also has to create and send out invalidation messages. We assume a packet creation time of 6 cycles for the first packet and 2 cycles for each additional invalidation packet that is sent out for the same request.

#### 4.5 Interconnection Networks

The various parameters that relate to the interconnection network include the topology of the network, the bandwidth of the network, the size of buffers in the various switches within the network and in the ports of the network, the speed of the network and the type of routing.

The different network topologies that we studied are the mesh, the hypercube and the shuffle-exchange network. The performance of the multiprocessor is measured as the network topology is varied. The networks are compared for two cases: (i) all the networks have the same channel bandwidth, and (ii) all the networks have the same bisection width. The channel width is varied between 4 bits and 64 bits (8 bytes), for all three network topologies. The bisection width of a network is the minimum number of wires that must be cut to divide the network into two equal halves [13]. Bisection width is a measure of network cost since the complexity of a connection topology is wire-limited. A 64-node mesh (8 x 8 grid), has a bisection width of 16 channels. A 64-node hypercube (6 dimensions), has a bisection width of 64 channels. A 64-node shuffle-exchange network, with a switch degree of 4 and a depth of 2, has a bisection width of 32 channels. In order to have the same bisection width in all network topologies, the channel width of the mesh can be four times the channel width of the hypercube and twice the channel width of the shuffle-exchange network.

We use the wormhole routing technique to route packets between nodes. For the mesh and the hypercube network we use the e-cube routing algorithm which is guaranteed to be deadlock-free and is deterministic [35]. The routing in the shuffle-exchange network is also deterministic. Deadlock-free adaptive routing algorithms have been proposed for wormhole routing [35]. These algorithms use extra channels. These may be extra physical channels or multiple virtual channels that share one physical channel. Both of these options are more expensive to implement when compared to deterministic routing. It remains to be seen whether adaptive routing gives better performance for realistic workloads.

The e-cube routing is dimension-ordered routing. For example, in the mesh network a packet is first routed in the X-direction until it reaches some node on the column on which the destination node is located. Then the packet travels in the Ydirection until it reaches the destination. In the case of the hypercube there are two nodes in each dimension. Starting with the lowest dimension, the packet is routed to the other node if the bits in the position corresponding to the current dimension in the source and destination node address differ. In the shuffle-exchange network the routing algorithm depends on the switch size. With a switch size of 4, the routing algorithm examines the destination address 2 bits at a time starting with the most significant bits first. The packet is routed to the output link selected by the two bits that is examined.

The network ports can buffer four packets. The directory module has buffer space that is used for packets waiting for a service to be completed, and also for packets waiting to enter the network when the port buffers are full. This in effect increases the port buffer space. In all our experiments we use a buffer space of 64 packets in the directory modules. The switch buffer size used in all experiments is 2 flits.

The speed of the network is assumed to be half that of the processor. That is, it takes two processor cycles to transfer a flit between two switches. The architecture simulated uses a pair of interconnection networks. One of them sends request packets and other receives replies. The two networks are necessary in order to avoid deadlocks. The network and the routing protocol in the network are guaranteed to be deadlock-free if the messages are consumed at the output. However, due to limited buffering in the directory module it cannot be guaranteed that the messages will always be consumed. The use of two networks avoids deadlocks by the following mechanism. First, the reply messages are always consumed because they are allocated dedicated buffer space when the request is sent out. Second, the request messages are serviced if there is buffer space in the module. The request messages are sent back as a reply with a negative acknowledgment if there is no buffer space in the module. Since there is not an infinite supply of requests (requests need to pre-allocate buffer space to receive the replies), and requests are turned into replies if they cannot be serviced

due to lack of buffer space and replies are always received from the network, there cannot be a deadlock.

The use of two physical networks can be avoided by multiplexing packets on a single network or by dropping packets that cannot be delivered and using a time-out mechanism to re-send these packets. Neither of these options are used in our simulation for the sake of simplicity.

## 4.6 Coherence Protocol

The coherence protocol simulated is write-back with invalidate. All simulations are sequentially consistent. It has been shown that better performance can be obtained with weaker consistency models. We feel that the performance of the network under sequential consistency should be studied, in order to understand the performance of the network when using various weaker consistency models. The study of the effect of network performance for a weakly consistent system is for future work.

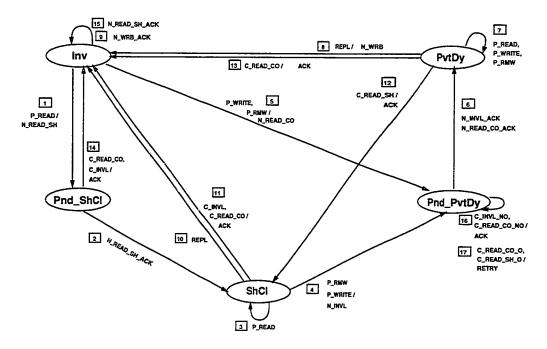

The Figure 4.2 shows the states of a line in the cache and the transactions involved. Each line in the cache can be in one of five states: Invalid (Inv), Shared-Clean (ShCl), Private-Dirty (PvtDy), Shared-Clean Pending (Pnd\_ShCl), and Private-Dirty- Pending (Pnd\_PvtDy). When the application is started all cache lines are invalid. The Figure 4.3 shows the states of a line in the directory module and the transactions involved. Each line in a directory module can be in one of four states: Uncached, Shared, Dirty, and Pending.

In both figures the transactions are labeled as follows: a prefix P\_ is used when the transaction originates at the processor. The prefix N\_ is used when the transaction originates at the cache and is sent through the network to the directory and the corresponding acknowledgment comes back from the directory. The prefix C\_ is used for all coherence requests originating from the directory module and sent to the caches.

Figure 4.2: State Diagram of the Write-Back Coherence Protocol

All transactions are labeled either X/Y or X, where X is the incoming request, and Y is the response.

The cache lines are initially invalid. On a read from the processor, a read request is sent to the directory module. When the read transaction is completed, the line is in the state Shared-Clean. On a write or a read-modify-write access from the processor, a write transaction is sent to the directory module. If a line in the directory module is in Uncached state, the read or the write transaction completes immediately. If the line is in Shared state, a read transaction can complete, whereas a write transaction will wait until all the copies of the cache line are invalidated. If the line in the directory module is in Dirty state, then the read or the write access cannot complete until a coherence access to the current owner of the line is completed. This access fetches the most recent copy of the data and also updates the state of the line at this cache to Shared-Clean or Invalid in the case of read or a write access respectively.

Figure 4.3: State Diagram Showing Different States of a Directory Line

There are certain coherence accesses that can happen in a system with a directory-based coherence protocol that will not happen in a snoopy coherence protocol implemented on a bus. This is due to the lack of global knowledge in a system with distributed memory. When a cache line load is pending from a read access, the cache can get a coherence access to invalidate the line. This can happen if the network does not guarantee ordered delivery, which is not the case in our simulation. This can also happen due to the presence of two networks in the systems. In this case the line is invalidated. When the reply arrives, the pending read is allowed to proceed but the line is not loaded in the cache. Any subsequent access to the same line would miss because the line was already invalidated.

When the cache is pending due to a write access, it can get an invalidate request. The directory might have sent the invalidate request before the directory processed this pending write or after. In the coherence protocol simulated, the directory tags the request such that the cache can determine whether this request came before or after the directory sends a reply to this module. In the former case it acknowledges

the coherence request and does not change its state (transaction 16 in Figure 4.2). This is because, the cache is certain that when the pending write returns the cache state will be restored. In the case that the request to invalidate the cache line was sent by the directory after the reply to this cache was sent out, the cache cannot acknowledge the invalidate access (transaction 17 in Figure 4.2). This is because the pending write access will change the data in the cache line. In this case the cache sends a message to the directory to retry the invalidate access.

This chapter has described the various parameters used in the simulations. The architecture simulated has 64 nodes, with a processor, a cache, a directory, and a memory module in each node. The system supports a write-back with invalidate coherence protocol, a full bit map directory, and sequential consistency.

# Chapter 5

## Results

This chapter presents the results of our study on the effect of the interconnection network on the performance of shared-memory multiprocessors. The architecture simulated and all the parameters of the architecture were presented in Chapter 4. Four network topologies: the mesh, the hypercube and two shuffle-exchange configurations, are studied at various network bandwidths. Section 5.1 gives a brief description of the applications used in our study. The following sections present the results obtained and a discussion of these results.

#### 5.1 Benchmarks

The benchmarks used should be representative of the projected workloads for the described architecture. The architecture is a scalable shared-memory multiprocessor. We expect the architecture, to be used like current message-passing multiprocessors, for compute intensive applications. The following algorithms were chosen from the numerical and non-numerical domains of study: Matrix Multiplication, Successive Over Relaxation, Fast Fourier Transform and Sorting.

Most of these algorithms use barriers for synchronization. Tournament barriers were implemented since they have relatively lower latency for the completion of the barrier ([24]). Conceptually, to achieve a barrier using this algorithm, processors start at the leaves of a binary tree with a fan-in of two. One processor from each node continues up the tree to the next "round" of the tournament. The processor reaching the root of the tree writes to a global flag on which all the other processors

are spinning. By contrast, the central barrier is implemented by having all processes increment a single global counter, which causes a lot of network traffic.

#### 5.1.1 Matrix Multiplication (MMULT)

The multiplication of two matrices involves mostly read-only sharing of data. Each process calculates the result for a square portion of the result matrix. Each process reads an eighth of each of the two input matrices in order to calculate a sixty-fourth of the result matrix. In this program one of the input matrices is transposed before the multiplication in order to increase locality in the caches. This way both matrices are accessed across rows. Multiplication of two 128x128 matrices is simulated.

The portion of the result matrix that is computed by each processor is also allocated to the memory module associated with that node. The two input matrices are allocated in similar sized blocks to each node. About seven-eighths of the total portion of the two input matrices read by a process are allocated on nodes that are remote to that process. A single barrier is used in the program to synchronize the processes after the transpose is completed.

#### 5.1.2 Successive Over Relaxation (SOR)

This is an iterative method of solving partial differential equations (see [38] for a description of the algorithm). Each computation depends only on its nearest neighbors. Hence active sharing is limited to the boundary elements. The program partitions data by blocks of rows. This program uses two matrices. During each iteration the data is read from one matrix and the results written to the next. During the next iteration the roles of the two matrices are switched, reading from the matrix previously written to and writing to the other matrix. We ran this program for a 256 x 256 matrix. Each data item is a double-precision floating point value. We ran

ten iterations of the program. While this is not enough to obtain convergence, the behavior of the algorithm is identical in all iterations after the cache has been filled.

The two matrices are partitioned by rows and allocated to the different memory modules. Four rows of each matrix are allocated to each memory module. Data is shared between neighboring processors in SOR. The synchronization is achieved by the use of locks. There is a lock associated with each shared row. Each lock is accessed by only two processors. This makes the lock-based implementation faster than having a barrier at the end of each iteration.

#### 5.1.3 Fast Fourier Transform (FFT)

The FFT program is based on the Cooley Tukey Radix-2 Decimation in Time algorithm. A general description of the algorithm can be found in [38]. The computation has  $log_2N$  stages, where N is the number of data points for which the FFT is computed. The processors synchronize with the help of a barrier at the end of each stage, for the first  $log_2P$  stages, where P is the number of processes doing the computation. The last  $log_2N - log_2P$  stages do not need synchronization since each process operates on the same data in every stage thereafter. Each data point consists of two double precision numbers, one for the real part and the other for the imaginary part. The experiments in this thesis were conducted for a data set size of 32,768 ( $2^{15}$ ) complex numbers.

The program uses two data sets, one of them holding the actual numbers to be transformed and the other holding a pre-computed set of sine values that is used during the computation. The entire data set is divided into sixty-four portions and the first portion is allocated to node zero and so on. During the first  $log_2P$  stages of the program, the processes are computing the transform on data that is not allocated at the local node. In this phase there is a lot of data movement across the network. During the remaining  $log_2N - log_2P$  stages of the FFT, the processes are operating

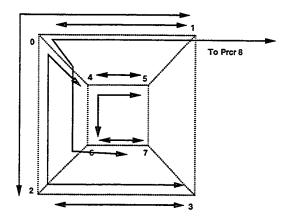

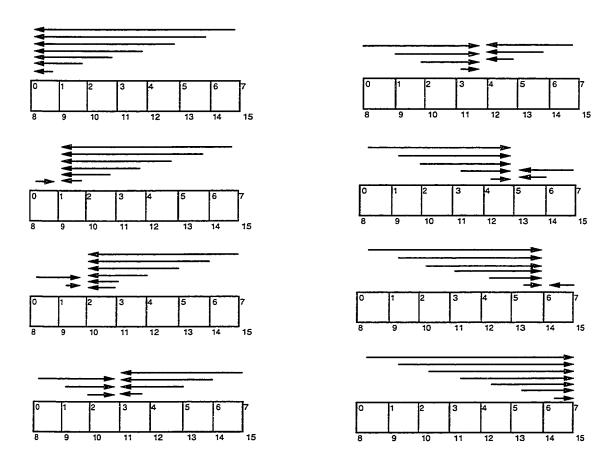

Figure 5.1: Communication Pattern of the FFT Algorithm

on data allocated to the local node. If this data fits in the cache, it will have a very high hit rate. Even if it does not, the miss penalty will be quite low. Figure 5.1 shows the communication pattern of the algorithm. One can see how this would map very well on a hypercube. The figure does not show the communication pattern of the pre-computed sine values.

## 5.1.4 Sorting (Bimerge)

Each process in this program sorts a pre-allocated sublist. The processes then proceed to merge the sorted sublists two at a time. A description of the algorithm can be found in [43]. During the merge phase all processors participate in the merging instead of a naive algorithm where in each subsequent merge phase only half the number of processors are involved in merging two previously merged sublists. The merge phase involves  $log_2P$  stages and there is a barrier synchronization after each stage. During each merge phase, the two lists that are being merged are split into as many sublists as there are processors participating in that merge phase. Then the cross over points between the sublists are determined and a parallel algorithm determines a pair of sublists that need to be merged. The merging of the pair of sublists that crossover is straightforward. We ran simulations for a data set size of 65,536 ( $2^{16}$ ) data points.

The data set is partitioned into 64 portions. The first portion is allocated to the memory module in node 0, etc. Each processor first sorts the array local to that processor. During the merging the amount of data communicated and the distance traveled by the data is dependent on the data itself. Since the merge phase does not update in place, there are actually two arrays used in the program.

The Table 5.1 gives a brief description of each program and the data set size.

| Application | Problem<br>Size                   | Shared Data<br>Space | Program Description                              |

|-------------|-----------------------------------|----------------------|--------------------------------------------------|

| MMULT       | 128 x 128                         | 196608 bytes         | Matrix Multiplication Successive Over Relaxation |

| SOR         | 256 x 256                         | 1048576 bytes        |                                                  |

| BIMERGE     | $2^{16}$ (65536) $2^{15}$ (32768) | 524288 bytes         | Merge Sort                                       |

| FFT         |                                   | 786432 bytes         | Fast Fourier Transform                           |

Table 5.1: Applications Used in Study

## 5.2 Effect of Network Topology

This section presents the results of our study on the effect of the interconnection network topology on the performance of shared-memory multiprocessors. A 64processor system was simulated. The network topologies studied were the hypercube, the mesh and the shuffle-exchange network. We ran experiments for two types of shuffle-exchange networks. In one case each switch was a 4x4 crossbar (SE4). This reduced the total number of stages in the network to 3. The other network used a 2x2 crossbar switch (SE2), making the total number of stages equal to 6 for a 64processor network. These particular topologies were chosen because we feel that they represent three very different types of networks. The mesh and hypercube are direct networks. They represent two ends of the spectrum of the group of networks called direct k-ary n-cubes. The shuffle-exchange network is an indirect network. It was chosen to see how it compared to some direct networks. The switch size of the network in a shuffle-exchange network trades contention against latency. We simulated two different switch sizes to see how this fares in a shared-memory multiprocessor. The performance of multiprocessors having different network topologies, each with constant channel width, were studied. The performance of the multiprocessor when the networks have a constant bisection width was also investigated.

## 5.2.1 Simulation of Networks with Constant Channel Width

The Figures 5.2 to 5.5 show the performance of the four different programs for different network topologies. Each graph has four curves showing the performance for the hypercube, mesh and the two shuffle-exchange networks. Each curve shows the execution cycles taken for each network topology when the channel width is varied between 4 bits and 64 bits. Table 5.2 shows the relative performance of these applications at a channel width of 4, 16 and 64 bits for the different network topologies.

|         | Program | HCube / | HCube / | HCube / | SE4 /   | SE2 /   | SE4 /  |

|---------|---------|---------|---------|---------|---------|---------|--------|

|         |         | Mesh(%) | SE4(%)  | SE2(%)  | Mesh(%) | Mesh(%) | SE2(%) |

| Link    | FFT     | 56.90   | 15.23   | 12.82   | 26.56   | 28.09   | -2.09  |

| Width   | BIMERGE | 14.00   | 18.03   | 11.44   | -3.53   | 2.25    | -5.58  |

| 4 bits  | SOR     | 0.85    | 24.32   | 2.93    | -23.28  | -2.07   | -17.20 |

|         | MMULT   | 2.28    | 2.33    | 4.09    | -0.04   | -1.73   | 1.68   |