pubs.acs.org/NanoLett

# Meniscus-Mask Lithography for Fabrication of Narrow Nanowires

Vera Abramova,<sup>†</sup> Alexander S. Slesarev,<sup>†</sup> and James M. Tour\*,<sup>†</sup>,<sup>‡,§,||</sup>

†Departments of Chemistry, ‡Materials Science and NanoEngineering, and §Computer Science and the <sup>||</sup>Smalley Institute for Nanoscale Science and Technology, Rice University, MS-222, 6100 Main Street, Houston, Texas 77005, United States

Supporting Information

ABSTRACT: We demonstrate the efficiency of meniscus-mask lithography (MML) for fabrication of precisely positioned nanowires in a variety of materials. Si, SiO<sub>2</sub>, Au, Cr, W, Ti, TiO<sub>2</sub>, and Al nanowires are fabricated and characterized. The average widths, depending on the materials, range from 6 to 16 nm. A broad range of materials and etching processes are used and the generality of approach suggests the applicability of MML to a majority of materials used in modern planar technology. High reproducibility of the MML method is shown and some fabrication issues specific to MML are addressed. Crossbar structures produced by MML demonstrate that junctions of nanowires could be fabricated as well, providing the building blocks required for fabrication of nanowire structures of varied planar geometry.

arrow metallic and semiconducting wires are important for purposes of miniaturization, addressing ultrasmall devices, and for exploiting properties of materials arising from spatial confinement such as band structure distortions and conductivity quantization. 1-3 Current nanowire fabrication methods can be divided into two major groups: bulk synthesis or lithographic. Bulk methods<sup>1,4–6</sup> allow for the synthesis of large quantities of individual nanowires, with control over their crystallinity and sometimes even crystallographic orientation. However, as there is no facile method to position an array of these wires on an integrated circuit plane, bulk synthetic methods are not suitable for integration into the modern planar technology used by the semiconductor industry. 1,7-11 In contrast, lithographical methods are widely used in industrial processes, but the resolution of conventional lithography is limited by the lithographic tool and resists, and making very fine features can be exceedingly costly. 12-14 Even though narrow nanowires can be fabricated by fine-tuned electron beam lithography, 14–16 doing this en masse is difficult. 14,17

A separate approach implemented, for example, in a sidewall image transfer technique, 17–19 uses deposition of the mask on

the sidewall of some pattern, as it gives precise control over the resulting nanowire width. Modern film deposition methods such as atomic layer deposition allow for control over the film thickness within a single atomic layer. However, deposition of material onto closely located sidewalls could be difficult due to shadowing and capillary effects.<sup>20–22</sup> Meniscus-mask lithography (MML) was shown for the fabrication of graphene nanoribbons.<sup>23</sup> This method is based on projection of either electron-beam or photolithography patterned sidewalls using adsorbed water as the mask. In this paper, we extend MML to a wide variety of metals, metal oxides, and semiconductors and further demonstrate that more complex structures, such as junctions and crossbars, can be fabricated. A particular advantage of the MML method is precise positioning of narrow nanowires that is required for large-scale device fabrication. The process could be directly integrated into modern planar technology with no modifications to existing

equipment and minimal changes in fabrication protocols. No new tools or materials are required.

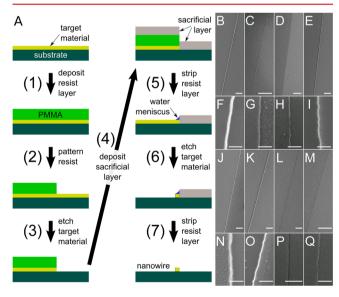

The general process scheme resembles the one described previously<sup>23</sup> and is schematically represented in Figure 1A. In a typical process a thin film of target material is covered with resist film (step 1) and patterned so that the edges of the pattern are located at the designated nanowire positions (step 2). Then, directional dry etching is performed (step 3) in order

Figure 1. MML fabrication of wires. (A) MML fabrication scheme. Examples of wires at low and high magnification SEM images: (B, F) Si wires; (C, G) SiO<sub>2</sub> wires; (D, H) Au wires; (E, I) Cr wires; (J, N) W wires; (K, O) Ti wires; (L, P) TiO2 wires; (M, Q) Al wires. The scale bars for images (B–E) and (J–M) are 1  $\mu$ m and for images (F–I) and (N-Q) are 100 nm.

Received: December 8, 2014 Revised: March 23, 2015 Published: March 31, 2015

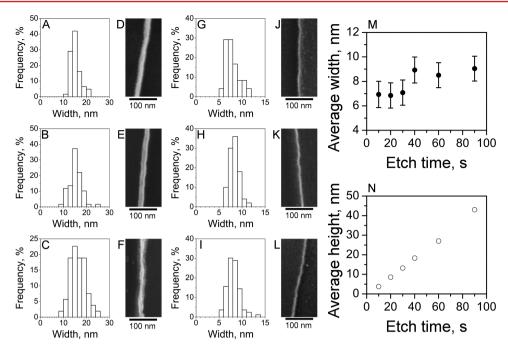

Figure 2. Si and  $SiO_2$  model wires produced with MML. (A–F) Width distribution and typical SEM images of Si wires fabricated with (A, D)  $Ar/Cl_2$  etching, (B, E)  $HBr/Cl_2$  etching, and (C, F)  $SF_6/O_2$  etching. (G–L) Width distribution and typical SEM images of  $SiO_2$  wires fabricated with (G, J)  $CHF_3/O_2$  etching, (H, K)  $CF_4/O_2$  etching, and (I, L)  $SF_6/O_2$  etching. (M–N) Variation of  $SiO_2$  (M) wires width and (N) height with etching time for  $SF_6/O_2$  etching.

to remove material exposed through the lithographic pattern. After that, the sacrificial metal layer is deposited (step 4) and the resist layer is stripped (step 5). Finally, a second directional dry etching is performed (step 6) and the material exposed through the sacrificial metal layer mask is etched, and then the sacrificial metal mask is wet etched (step 7). During the second dry etching (step 6), the narrow region nearby the sacrificial metal mask is protected by a thin adsorbed water layer, which is slightly thicker nearby the wedge, <sup>23</sup> resulting in consistent formation of long, narrow, precisely positioned nanowires of the target material. The contact area of water depends on the target material. Hydrophobic materials, such as the PMMA resist layer, do not form a meniscus.

The MML process could be used to fabricate the wires out of a number of materials (Figure 1). We have successfully prepared Si wires (Figure 1B,F), SiO<sub>2</sub> wires (Figure 1C,G), Au wires (Figure 1D,H) with an average width of 7.0  $\pm$  1.0 nm, Cr wires (Figure 1E,I) with an average width of 11.4  $\pm$  1.0 nm, W wires (Figure 1J,N) with an average width of 15.9  $\pm$  1.0 nm, Ti wires (Figure 1K,O) with an average width of  $9.8 \pm 1.0$  nm,  $TiO_2$  wires (Figure 1L,P) with an average width of 10.9  $\pm$  1.0 nm, and Al wires (Figure 1M,Q) with an average width of 6.9  $\pm$ 1.0 nm. Additionally, we previously reported similar fabrication of Pt wires (average width  $11.7 \pm 1.0$  nm).<sup>23</sup> The Si wires are presented in detail in Figure 2 and the resulting discussion. The etching conditions utilized and other fabrication details are summarized in Supporting Information Tables S1-S3. The distributions of wire widths are shown in Supporting Information Figure S1, and detailed statistical parameters of resulting wires are summarized in Supporting Information Table S4. Typical AFM images of MML fabricated nanowires are shown in Supporting Information Figure S2. The nanowires' height is uniform over their length and is equal to or slightly exceeding the thickness of the starting target material film.

In order to demonstrate the versatility of the MML fabrication method, we have thoroughly analyzed the critical process step, the dry etching, demonstrating the water meniscus mask stability against different types of plasma processes. Reactive ion etching (RIE) is a conventionally accepted term for all plasma etching processes; however, there are several different phenomena occurring in plasma discharges leading to materials etching: (1) physical sputtering when the target material gets removed from the substrate due to bombardment with highly energetic ions, (2) chemical etching when plasma species react with the target material on their own, (3) ionenhanced energetic etching when plasma species react with the substrate only if sufficiently accelerated toward it, and (4) ionenhanced inhibitor etching when plasma species cause the formation of a protective inhibitor layer everywhere except the areas exposed to ion flux.<sup>24</sup> All of those mechanisms are directional except chemical etching, which works isotropically. Methods relying solely on physical sputtering are easily distinguishable from chemically assisted directional plasma etching. However, ion-enhanced energetic and ion-enhanced inhibitor mechanisms typically coexist in directional dry etching processes.

The typical example of physical sputtering removal of material is etching of noble metals (Au, Pt) with Ar plasma. Sputtering works on diverse materials, however, the typical etch rates are low,<sup>24</sup> and other etching processes are usually preferred for chemically active materials. Redeposition is a common problem for physical sputtering and occurs when sputtered substrate atoms/clusters are not removed from the system but return to the substrate or stick to the mask walls.<sup>25,26</sup> Although we successfully fabricated narrow Au and Pt wires in the MML process, their yield was limited by random formation of much thicker irregular objects (Supporting Information Figure S3), which we attributed to redeposition effects. The size of those objects suggests they were mostly

formed during the first etching step, and indeed we were able to mitigate this problem by adjusting the lithography conditions to make the PMMA sidewall slope outward enabling better removal of sputtered material.

Unlike sputtering, which is always directional, the chemically assisted dry etching processes are characterized both by the etch rate and the undercut, which is the relative impact of isotropic etching, that is, the etching that occurs in a direction parallel to the substrate. For MML fabrication of narrow wires, highly directional processes are desired, as the undercut affects the width of the resulting wires up to their complete disappearance. Unlike the exact process mechanism, undercutting is well documented for different plasma etching processes. Preferred compositions of plasma are well known for various materials. For example, fluorine-based plasmas are widely used to etch Si (refs 27 and 28), SiO<sub>2</sub> (refs 29 and 30), W (ref 31), Ti (ref 32), and TiO<sub>2</sub> (ref 33), whereas chlorinebased plasmas are used for etching of Si (refs 27, 28, and 34), W (ref 17), Al (ref 35), and Cr (ref 36). We have found that wire formation occurs independent of the exact directional etching mechanism for all those systems (Figure 1).

In some particularly aggressive plasmas, such as  $\text{Cl}_2/\text{O}_2$  or  $\text{Cl}_2/\text{O}_2/\text{N}_2$  etching of Cr, and  $\text{Cl}_2/\text{Ar}$  etching of W, the important issue of resist erosion<sup>37</sup> manifested itself in the formation of shelf-like structures adjacent to the wire (Supporting Information Figure S4). It is observed on the side of the wire exposed in the first etching step and could not be avoided simply by increasing the first etching time. We were able to ameliorate this effect by adding a physical sputtering step immediately after the first etching step, as sputtering does not withdraw the resist edge and removes residuals of exposed metal that otherwise would form the shelf.

In order to compare the effect of different etching methods on nanowire formation, we used Si and  $\mathrm{SiO}_2$  as model systems. The etching of these materials is well studied; they are readily available commercially in the form of silicon-on-insulator and thermal  $\mathrm{SiO}_2$  coated Si wafers and they have smooth uniform surfaces.

Figure 2A-F shows the width distributions and corresponding typical SEM images of Si wires prepared with different etching processes. The average width of Si wires is  $15.2 \pm 1.0$ nm for Ar/Cl<sub>2</sub> etching,  $15.4 \pm 1.1$  nm for HBr/Cl<sub>2</sub> etching, and  $16.4 \pm 1.1$  nm for SF<sub>6</sub>/O<sub>2</sub> etching. In the Ar/Cl<sub>2</sub> process, an impenetrable nonvolatile layer of SiCl<sub>x</sub> is formed on the Si surface, and the directional process results from argon ion bombardment volatilizing  $SiCl_x$  from the bottom.<sup>24,27</sup> The process of HBr/Cl<sub>2</sub> etching is similar, but the passivating layer contains Br as well.<sup>27</sup> In the SF<sub>6</sub>/O<sub>2</sub> process, the SiO<sub>x</sub>F<sub>y</sub> film is sputtered from the bottom and redeposited on the sidewalls resulting in directionality etching.  $^{24,27,28}$  For the SF<sub>6</sub>/O<sub>2</sub> etching procedure, we measured a wider wire width distribution than for other procedures; however, the average wire widths for all three etching methods are very close, indicating that the exact etching mechanism or chemistry involved do not significantly affect the result.

Figure 2G–L shows the width distributions and corresponding typical SEM images for  $SiO_2$  wires prepared with different etching processes and in different etching instruments. The average width of  $SiO_2$  wires is 7.9  $\pm$  1.0 nm for  $CHF_3/O_2$  etching, 8.3  $\pm$  1.0 nm for  $CF_4/O_2$  etching, and 8.0  $\pm$  1.0 nm for  $SF_6/O_2$  etching. All three processes result in formation of passivating layers on the walls of etched trenches; however, the composition of these passivating layers is different.  $^{17,28}$  Also,

the  $\mathrm{CHF_3/O_2}$  and  $\mathrm{CF_4/O_2}$  processes work through formation of a fluorocarbon film on the etched plane, <sup>17</sup> whereas the  $\mathrm{SF_6/O_2}$  process depends mostly on fluorine reactivity. <sup>24,28</sup> The width distributions of wires fabricated using those different processes, however, are similar. Moreover, these results were reproduced in four different RIE instruments, thereby exemplifying the method reproducibility.

For the  $SF_6/O_2$  etching process, we have tested the wire cross section evolution with etching time. Figure 2M shows the average width of the wires, which do not change significantly, and Figure 2N shows the average height of the wires, which increases linearly with etching time. This suggests that the water mask is sufficiently stable to provide wires of arbitrary height over a wide range. This formation of arbitrary height wires comes with certain requirements: (1) the etching procedure needs to be adjusted so as not to damage the resist or sacrificial metal mask before the desired etch depth is achieved and (2) the process undercut is minimal.

In order to verify the apparent continuity of the wires and to characterize their electronic transport behavior, we patterned leads onto the wires (Supporting Information Figures S5–S7). Most types of wires (Au, Ti, Cr, W, Si) were conductive, and Si wires were operating as FET devices when backgated by the handling Si layer (Supporting Information Figure S7). However, for native oxide forming metals (Ti, Cr, W), the conductivity was several orders of magnitude lower than expected, which could originate from oxidation of the outer wire region. Al wires were found to be nonconductive, most probably for the same reason.

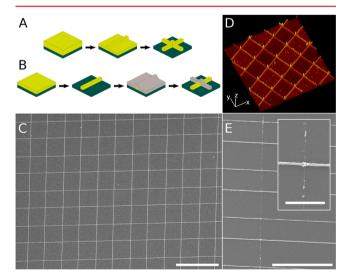

The fabrication method that we demonstrated here permits not only arbitrary shaped individual wires or parallel arrays of those, but also crossbars of wires, both homogeneous with the same material wires intersecting (Figure 3A), and heteroge-

Figure 3. Crossbar structures prepared with MML. (A–B) Schematics of crossbar structure fabrication for (A) homogeneous (both wires are made out of the same material) and (B) heterogeneous (wires are made of different materials) crossbars. (C) SEM image of homogeneous  $\text{SiO}_2-\text{SiO}_2$  crossbars. Scale bar is 5  $\mu$ m. (D) AFM image of homogeneous  $\text{SiO}_2$  crossbars. Scale bars are (x) 1  $\mu$ m, (y) 1  $\mu$ m, (z) 125 nm. (E) SEM image of heterogeneous Si–Pt crossbar structure (Si horizontal, Pt vertical). Scale bar is 5  $\mu$ m. Inset: magnified image of individual wire intersection. Note that bright speckles on Pt wire are traces of redeposition; the actual Pt wire is a thin vertical line on the image (see text). Scale bar is 1  $\mu$ m.

neous with different wire materials wires intersecting (Figure 3B). SiO<sub>2</sub>/SiO<sub>2</sub> homogeneous crossbar structures (Figure 3C<sub>2</sub>D and Supporting Information Figure S8) were prepared by repeating the same MML fabrication sequence twice, one pattern array perpendicular to another. The magnified image of the intersection site (Supporting Information Figure S8A inset) shows that intersecting wires are connected. The AFM image (Figure 3D and Supporting Information Figure S8B,C) shows that both wires have approximately the same height, and the intersection point is elevated by the height of one wire over another wire, thus twice that elevated over the bottom of the chip. The structure could also be interpreted as a regular array of narrow tips. A Si/Pt heterogeneous crossbar structure (Figure 3E) was prepared by depositing Pt onto an array of MML fabricated nanowires and repeating the MML procedure with a pattern perpendicular to the Si wires. Bright speckles on Pt wire are traces of redeposition, which was significant here in both etching steps of Pt wire preparation, as the Si wires height is ~100 nm; the actual Pt wire is a thin vertical line on the

In conclusion, we demonstrated that the MML approach is suitable for the fabrication of narrow nanowires from Si, SiO<sub>2</sub>, Au, Cr, W, Ti, TiO<sub>2</sub>, Al. A range of materials and etching processes suggest the applicability of MML to a wide array of materials used in modern planar technology. We also discussed some fabrication difficulties specific to materials and processes used and demonstrated that they could be avoided. Crossbar structures show that junctions of nanowires could also be fabricated. Thus, MML provides the building blocks required for fabrication of a host of nanowire structures over various geometries.

Methods. Metal wire samples were made using polished, single-sided, heavily p-doped Si wafers with a 300 nm thermal SiO<sub>2</sub> layer (Silicon Quest International) as substrates. Starting metal films were deposited onto substrates via sputtering (Denton Desk V Sputter system) or e-beam evaporation. These Si/SiO<sub>2</sub> substrates were also used as a starting film in preparation of SiO<sub>2</sub> nanowires. Silicon on insulator (SOI) wafers with a 100 nm p-doped (100) oriented device layer (resistivity 8.5–11.5  $\Omega$ ·cm), a 200 nm oxide layer and a 500  $\mu$ m heavily p-doped handling layer were used as a starting material for Si nanowire fabrication. TiO2 films were deposited on Si/ SiO<sub>2</sub> wafers using an atomic layer deposition system (courtesy of Dr. M. Thomas and Dr. P. J. Joseph, Georgia Tech University). Electron-beam lithography patterning and SEM imaging were performed using a JEOL 6500F scanning electron microscope. Images were acquired at a 15 kV accelerating voltage in SE mode with no additional conductive coating applied. Lithography patterns were written using PMMA 950 A resist at 30 kV accelerating voltage and 300 pA beam current. Reactive ion etching was performed using a Trion RIE instrument, Oxford RIE 80 instrument, Oxford ICP 100 instrument and 790 Plasma Therm RIE instrument. A detailed description of etching conditions is given in the Supporting Information section.

#### ASSOCIATED CONTENT

## **S** Supporting Information

Further details are provided on fabrication procedures, statistical analysis of nanowire width distributions, defects caused by material redeposition and mask erosion, and nanowires' conductivity. This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

### **Corresponding Author**

\*E-mail: tour@rice.edu.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

Authors thank the University of Texas Microelectronics Research Center and University of Houston Nanofabrication Facility for access to clean room equipment, and Dr. M. Thomas and Dr. P. J. Joseph, Georgia Tech University for ALD preparation of  $\text{TiO}_2$  wafers. This work was funded through the Air Force Office of Scientific Research (FA9550-14-1-0111).

#### REFERENCES

- (1) Law, M.; Goldberger, J.; Yang, P. Annu. Rev. Mater. Res. 2004, 34, 83-122.

- (2) Li, Y.; Qian, F.; Xiang, J.; Lieber, C. M. Mater. Today 2006, 9, 18-27

- (3) Dasgupta, N. P.; Sun, J.; Liu, C.; Brittman, S.; Andrews, S. C.; Lim, H.; Cao, H.; Yan, R.; Yang, P. Adv. Mater. 2014, 26, 2137–2184.

- (4) Xia, Y.; Yang, P.; Sun, Y.; Wu, Y.; Mayers, B.; Gates, B.; Yin, Y.; Kim, F.; Yan, H. Adv. Mater. 2003, 15, 353–389.

- (5) Shi, J.; Wang, X. J. Vac. Sci. Technol., B: Nanotechnol. Microelectron.: Mater., Process., Meas., Phenom. 2011, 29, 060801.

- (6) Chen, J.; Wiley, B. J.; Xia, Y. Langmuir 2007, 23, 4120-4129.

- (7) Lu, W.; Lieber, C. M. J. Phys. D: Appl. Phys. 2006, 39, R387-R406.

- (8) Haselman, M.; Hauck, S. Proc. IEEE 2010, 98, 11-38.

- (9) Long, Y.-Z.; Yu, M.; Sun, B.; Gu, C.-Z.; Fan, Z. Chem. Soc. Rev. 2012, 41, 4560-4580.

- (10) Liu, X.; Long, Y.-Z.; Liao, L.; Deng, X.; Fan, Z. ACS Nano 2012, 6, 1888–1900.

- (11) Kwiat, M.; Cohen, S.; Pevzner, A.; Patolsky, F. Nano Today 2013, 8, 677-694.

- (12) Bratton, D.; Yang, D.; Dai, J.; Ober, C. K. Polym. Adv. Technol. 2006, 17, 94-103.

- (13) Zimmerman, P. A.; Rice, B. J.; Piscani, E. C.; Liberman, V. In *Proc. SPIE 7274, Optical Microlithography XXII*; ; Levinson, H. J., Dusa, M. V., Eds.; SPIE, San Jose, CA, 2009, p 727420.

- (14) Grigorescu, A. E.; Hagen, C. W. Nanotechnology 2009, 20, 292001

- (15) Manfrinato, V. R.; Zhang, L.; Su, D.; Duan, H.; Hobbs, R. G.; Stach, E. A.; Berggren, K. K. *Nano Lett.* **2013**, *13*, 1555–1558.

- (16) Lee, S. W.; Sankaran, R. M. Mater. Today 2013, 16, 117-122.

- (17) Donnelly, V. M.; Kornblit, A. J. Vac. Sci. Technol. A 2013, 31, 050825.

- (18) Liebmann, L.; Kye, J.; Kim, B.-S.; Yaun, L.; Geronimi, J.-P. Proc. SPIE 7641, Design for Manufacturability through Design-Process Integration IV; Rieger, M. L., Thiele, J., Eds.; SPIE, San Jose, CA, 2010, p 764105.

- (19) Bencher, C.; Dai, H.; Miao, L.; Chen, Y.; Xu, P.; Chen, Y.; Oemardani, S.; Sweis, J.; Wiaux, V.; Hermans, J.; Chang, L.-W.; Bao, X.; Ye, H.; Wong, H.-S. P. *Proc. SPIE 7973, Optical Microlithography XXIV*, 79730K; Dusa, M. V., Ed.; SPIE, San Jose, CA, 2011.

- (20) Carlson, A.; Liu, T.-J. K. *Proc. SPIE 6924, Optical Microlithography XXI*; Levinson, H. J., Dusa, M. V., Eds.; San Jose, CA, USA, 2008, p 69240B.

- (21) Kawasaki, H.; Basker, V. S.; Yamashita, T.; Lin, C.-H.; Zhu, Y.; Faltermeier, J.; Schmitz, S.; Cummings, J.; Kanakasabapathy, S.; Adhikari, H.; Jagannathan, H.; Kumar, A.; Maitra, K.; Wang, J.; Yeh, C.-C.; Wang, C.; Khater, M.; Guillorn, M.; Fuller, N.; Chang, J.; Chang, L.; Muralidhar, R.; Yagishita, A.; Miller, R.; Ouyang, Q.; Zhang, Y.; Paruchuri, V. K.; Bu, H.; Doris, B.; Takayanagi, M.; Haensch, W.; McHerron, D.; O'Neill, J.; Ishimaru, K. *Electron Devices Meeting*; IEEE, Baltimore, MD, USA, 2009.

(22) Cai, X.; Xie, R.; Cheng, K.; Khakifirooz, A. U.S. Patent 20140191324A1, July 10, 2014.

- (23) Abramova, V.; Slesarev, A. S.; Tour, J. M. ACS Nano 2013, 7, 6894-6898.

- (24) Flamm, D. L. Pure Appl. Chem. 1990, 62, 1709-1720.

- (25) Smith, R.; Tagg, M. A.; Walls, J. M. Vacuum 1984, 34, 175-180.

- (26) Franz, G.; Kachel, R.; Sotier, S. Mater. Sci. Semicond. Process. 2002, 5, 45-50.

- (27) Rangelow, I. W.; Löschner, H. J. Vac. Sci. Technol., B: Microelectron. Nanometer Struct.—Process., Meas., Phenom. 1995, 13, 2394—2399.

- (28) Jansen, H.; Gardeniers, H.; de Boer, M.; Elwenspoek, M.; Fluitman, J. J. Micromech. Microeng. 1996, 6, 14–28.

- (29) Rueger, N. R.; Doemling, M. F.; Schaepkens, M.; Beulens, J. J.; Standaert, T. E. F. M.; Oehrlein, G. S. J. Vac. Sci. Technol., A 1999, 17, 2492–2502.

- (30) Williams, K. R.; Muller, R. S. J. Microelectromech. Syst. 1996, 5, 256-269.

- (31) Picard, A.; Turban, G. Plasma Chem. Plasma Process. 1985, 5, 333-351.

- (32) Fracassi, F.; d'Agostino, R. Pure Appl. Chem. 1992, 64, 703-707.

- (33) Setyawati, O.; Engenhorst, M.; Bartels, M.; Daneker, V.; Wittzack, S.; Woit, T.; Köhler, F.; Hillmer, H. J. Micro/Nanolithogr., MEMS, MOEMS 2010, 9, 041110.

- (34) Pogge, H. B.; Bondur, J. A.; Burkhardt, P. J. J. Electrochem. Soc. **1983**, 130, 1592–1597.

- (35) Bell, H. B.; Anderson, H. M.; Light, R. W. J. Electrochem. Soc. 1988, 135, 1184-1191.

- (36) Kornblit, A.; Novembre, A. E. U.S. Patent 5948570, Sept. 7, 1999.

- (37) Flamm, D. L.; Donnelly, V. M. Plasma Chem. Plasma Process. 1981, 1, 317–363.